FEMFET device and method for producing same

A field-effect transistor, ferroelectric memory technology, applied in the fields of electric solid state devices, semiconductor/solid state device manufacturing, transistors, etc., can solve problems such as increasing the risk of electrical breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

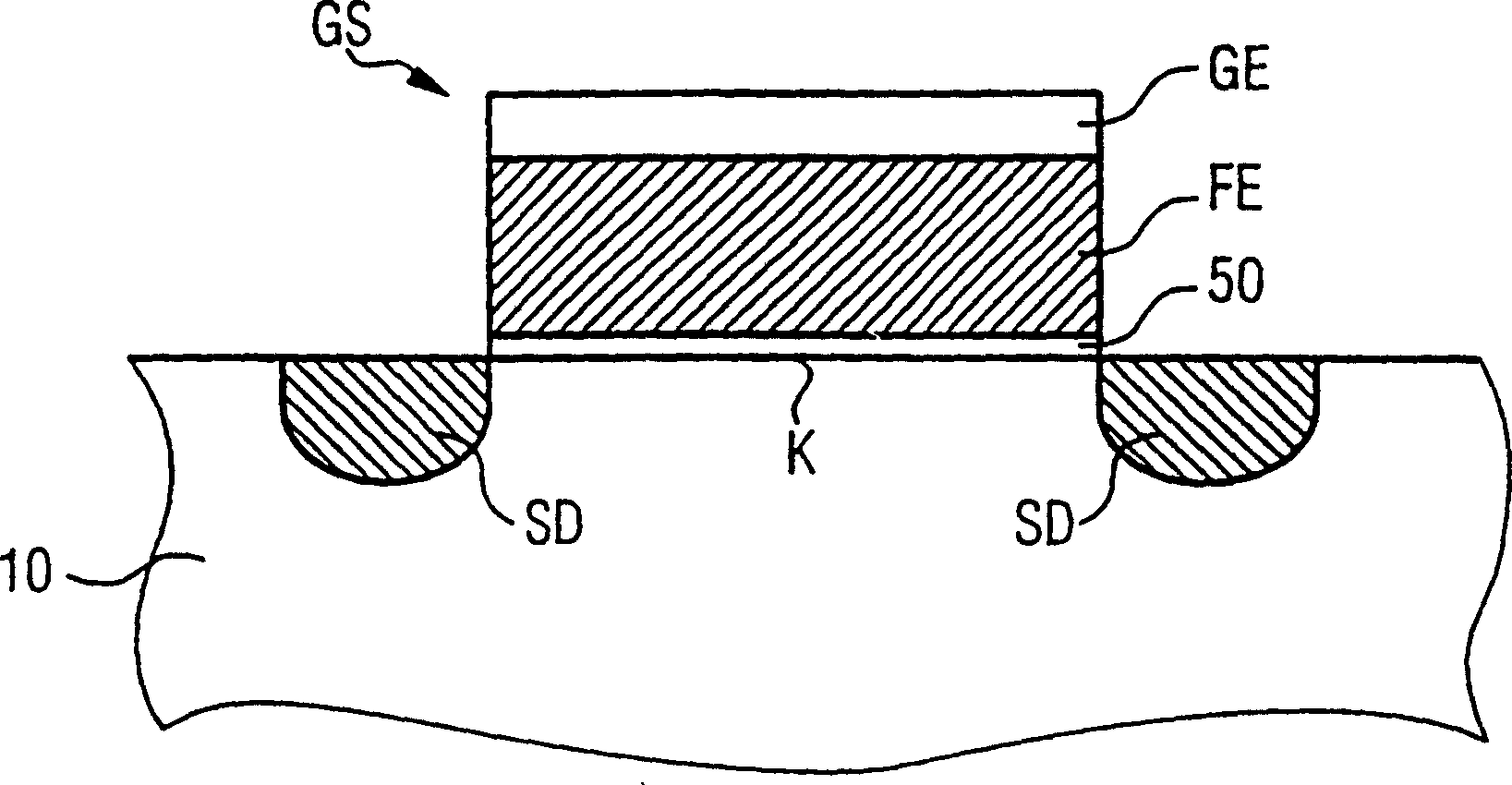

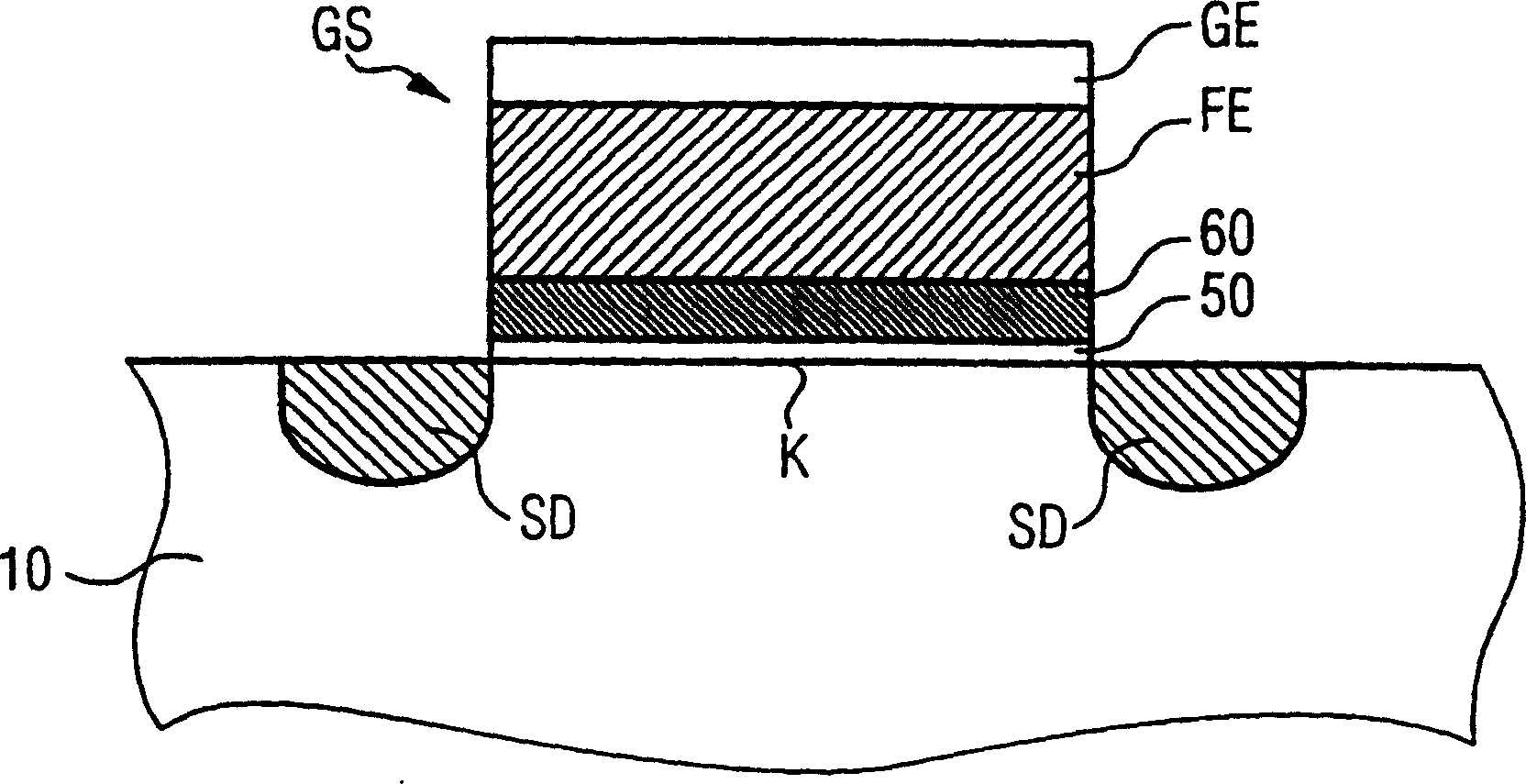

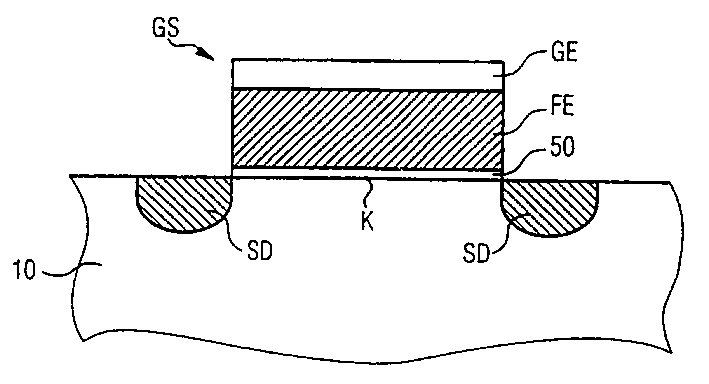

[0027] exist figure 1 Among them, 10 represents the semiconductor substrate, S represents the source region, D represents the drain region, K represents the channel region, GS represents the gate stack, 50 represents the diffusion barrier layer, FD represents the ferroelectric layer and GE means gate.

[0028] High-purity interfaces and silicon nitride (Si 3 N 4 ) combination as a diffusion barrier layer. In modern units, adding hydrofluoric acid vapor to the surface of the substrate can eliminate the natural oxide (SiO2) present on the semiconductor substrate 10. 2 ), followed by Si 3 N 4 The sputtering is carried out without exposing the semiconductor substrate to an oxidizing atmosphere during the two process steps. Therefore, Si can be 3 o 4 Sputtering directly on the semiconductor substrate 10 without having to endure the formation of oxides, especially SiO 2 The reality, depending on the specific circumstances, may also be a ceramic oxide (CeO 2 , Y 2 o 3 , Z...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap