Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7 results about "Volatile memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Volatile memory, in contrast to non-volatile memory, is computer memory that requires power to maintain the stored information; it retains its contents while powered on but when the power is interrupted, the stored data is quickly lost.

Methods for upgrading, diagnosing, and maintaining replaceable non-volatile memory

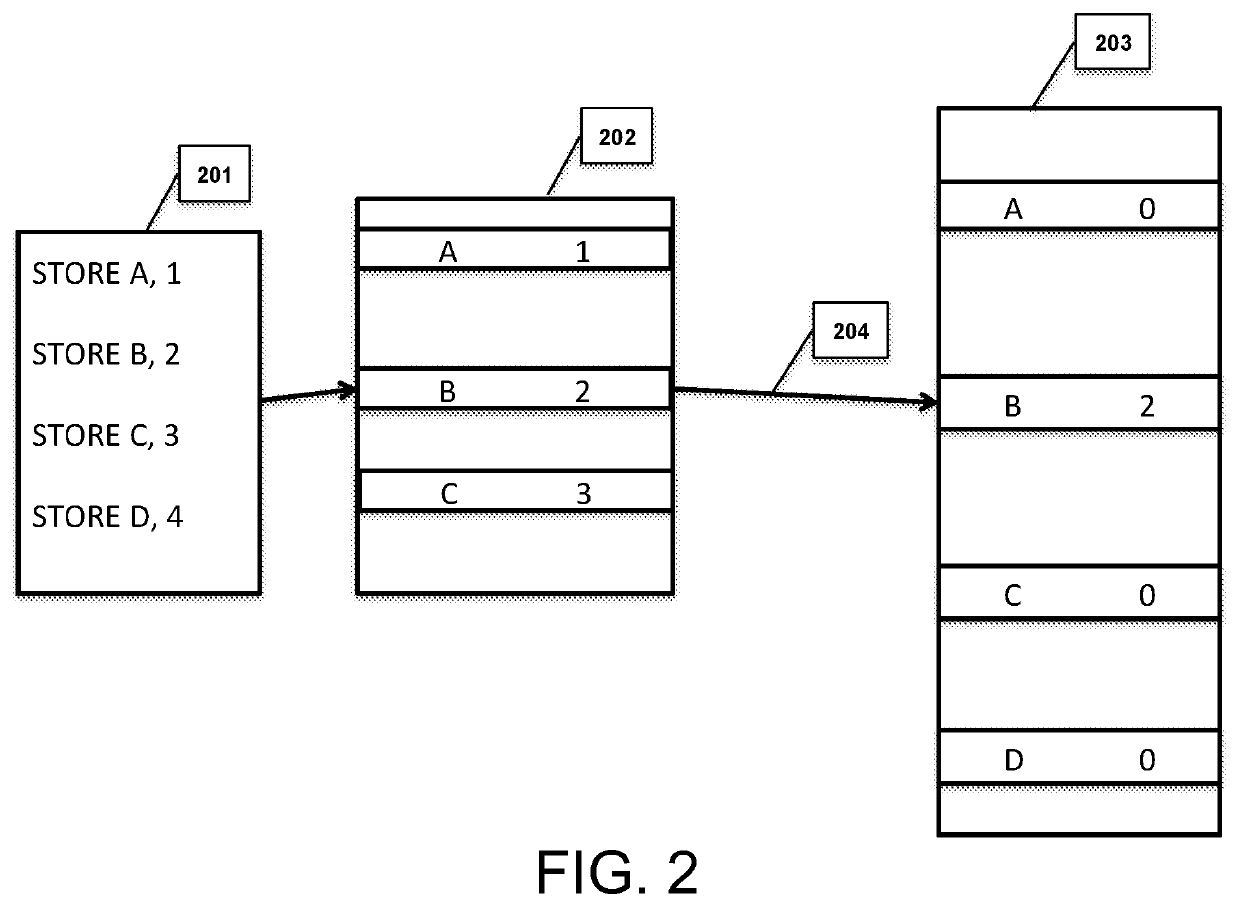

In one embodiment of the invention, a replaceable memory apparatus is disclosed. The replaceable memory apparatus includes a first rectangular multilayer printed circuit board having a first side and a second side opposite the first side; a first male pluggable electrical connector mounted to the first side near a first edge; a first female pluggable electrical connector mounted to the second side; and first non-volatile memory mounted to the first side and the second side. The first female pluggable electrical connector is coupled to the first male pluggable electrical connector to feed through first signals. The first non-volatile memory is coupled to the first female pluggable electrical connector and the first male pluggable electrical connector to receive the first signals.

Owner:WESTERN DIGITAL TECH INC

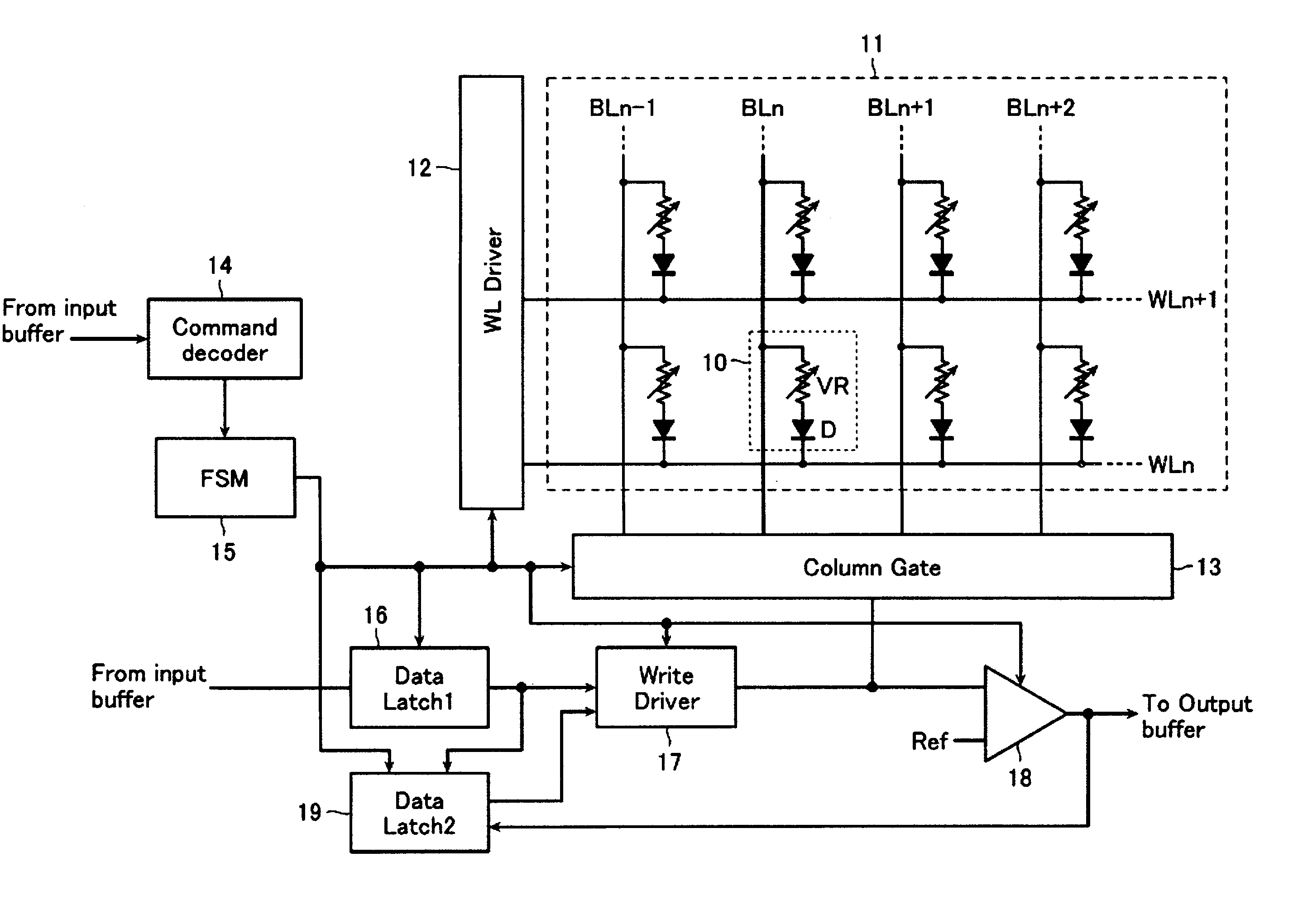

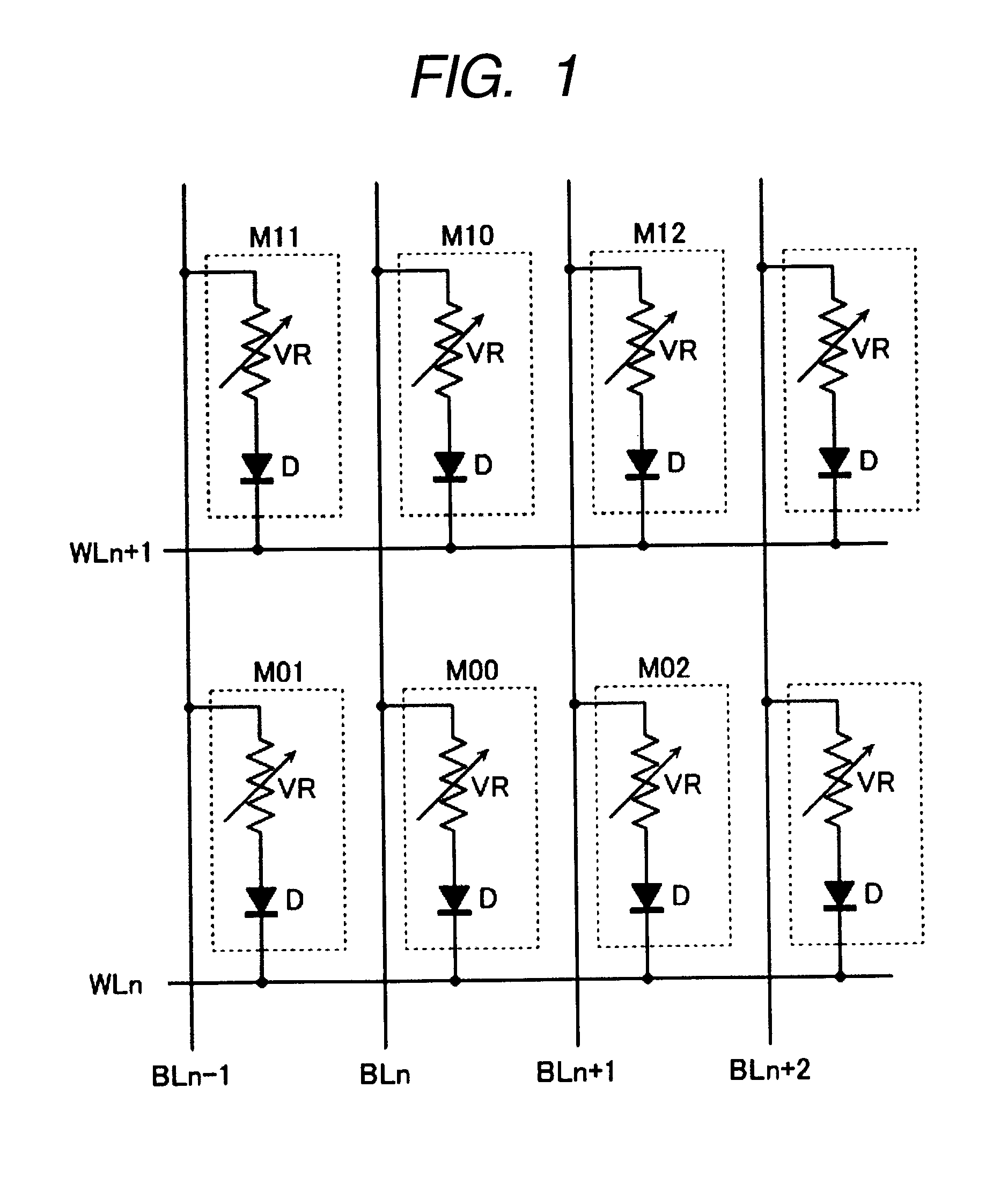

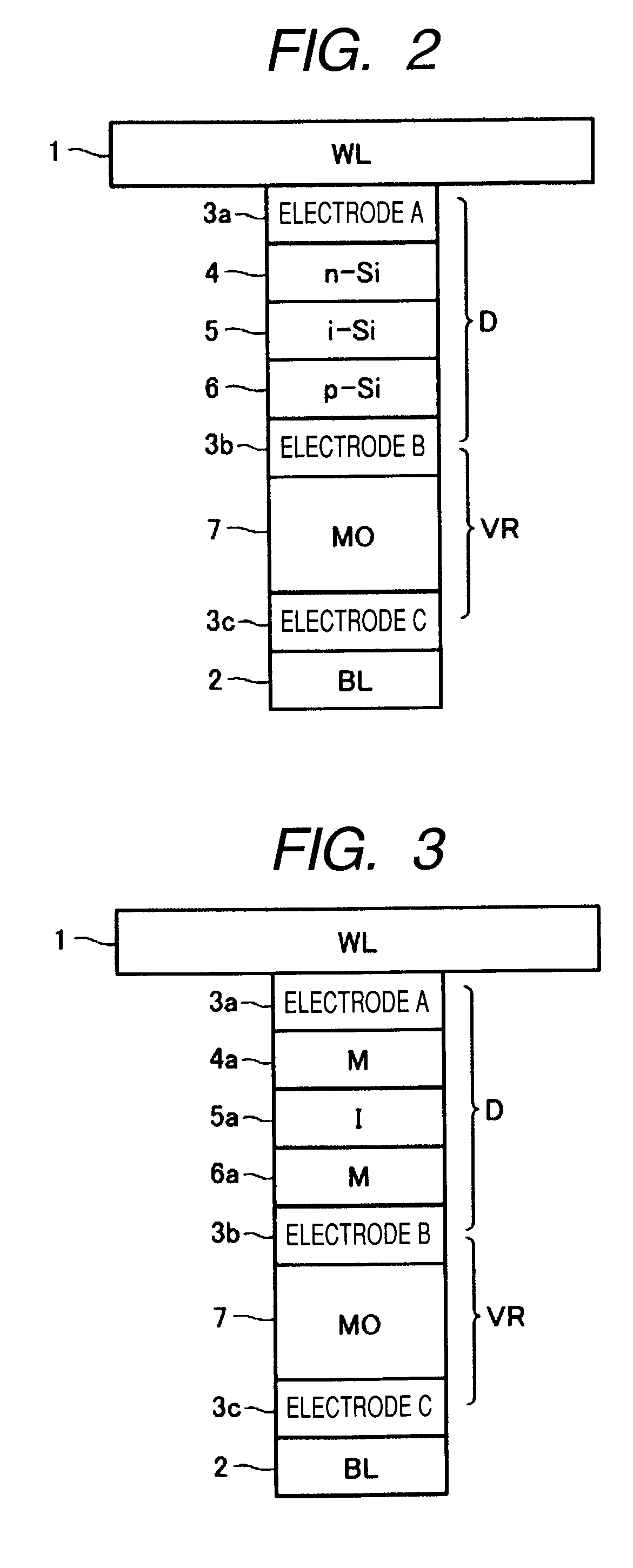

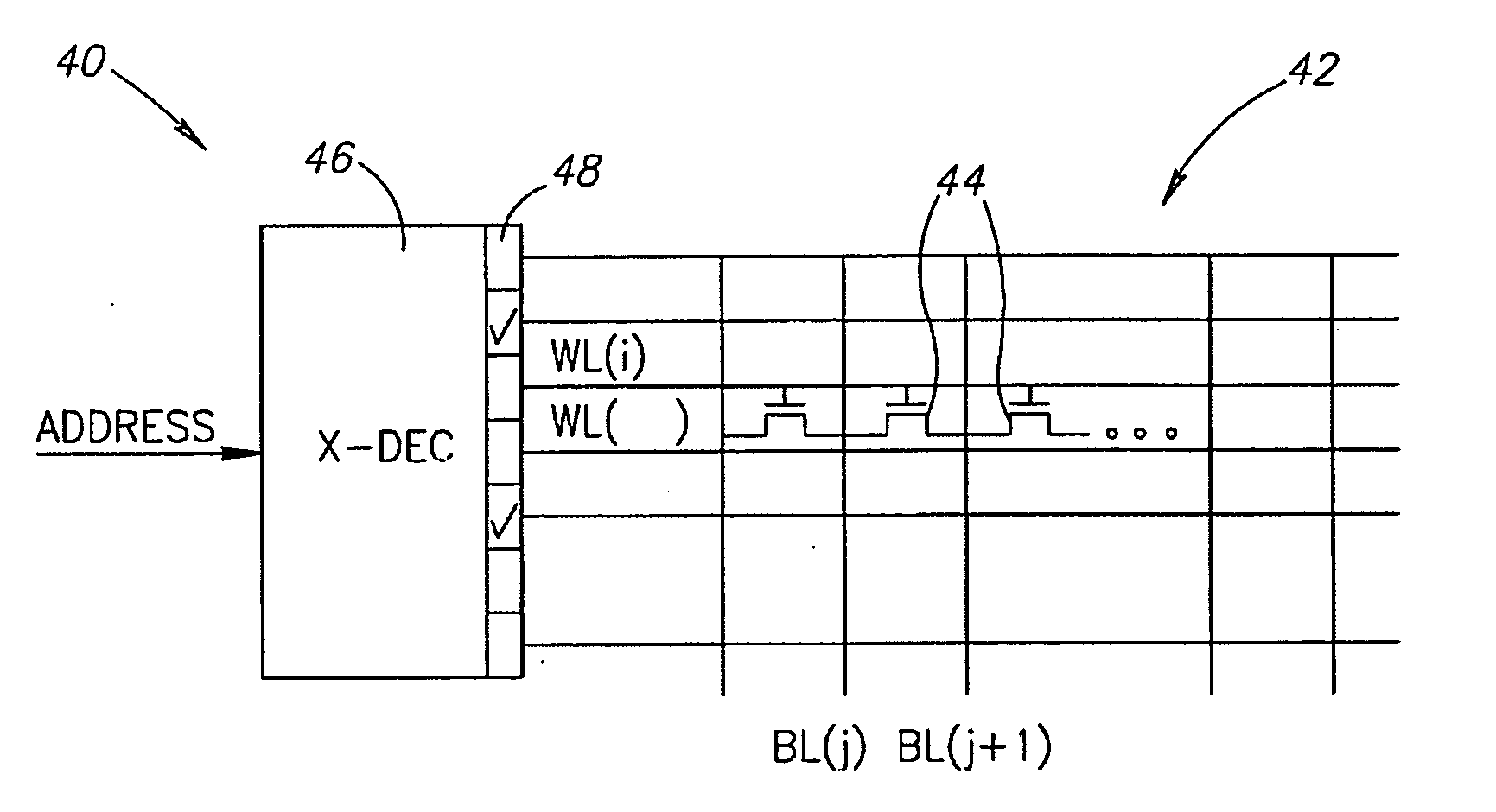

Non-volatile memory device

Owner:KIOXIA CORP

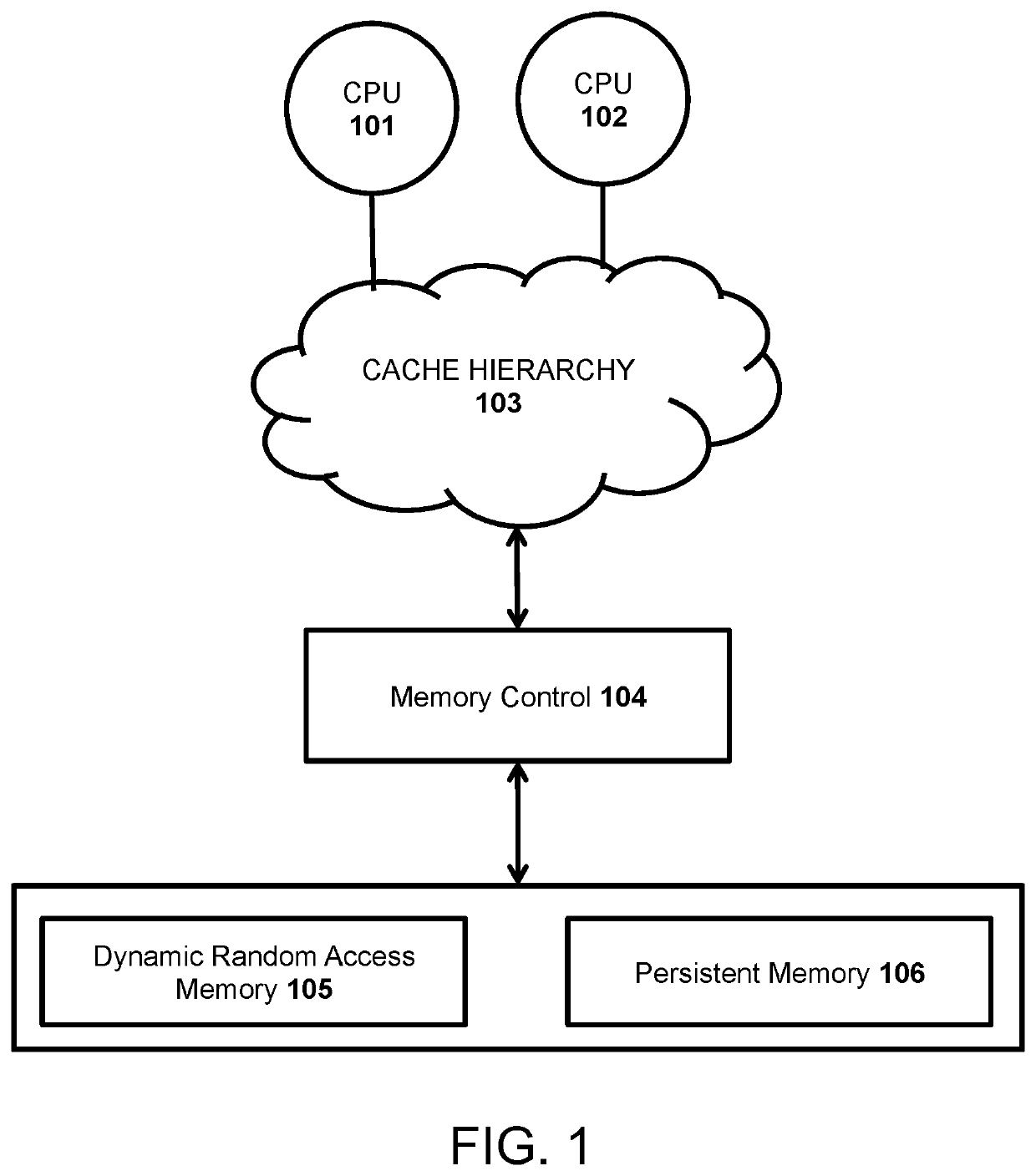

System and method for persisting hardware transactional memory transactions to persistent memory

ActiveUS10956324B1Atomicity of operationDurability of write operationMemory architecture accessing/allocationConcurrent instruction executionComputer architectureConcurrency control

Owner:GILES ELLIS ROBINSON +1

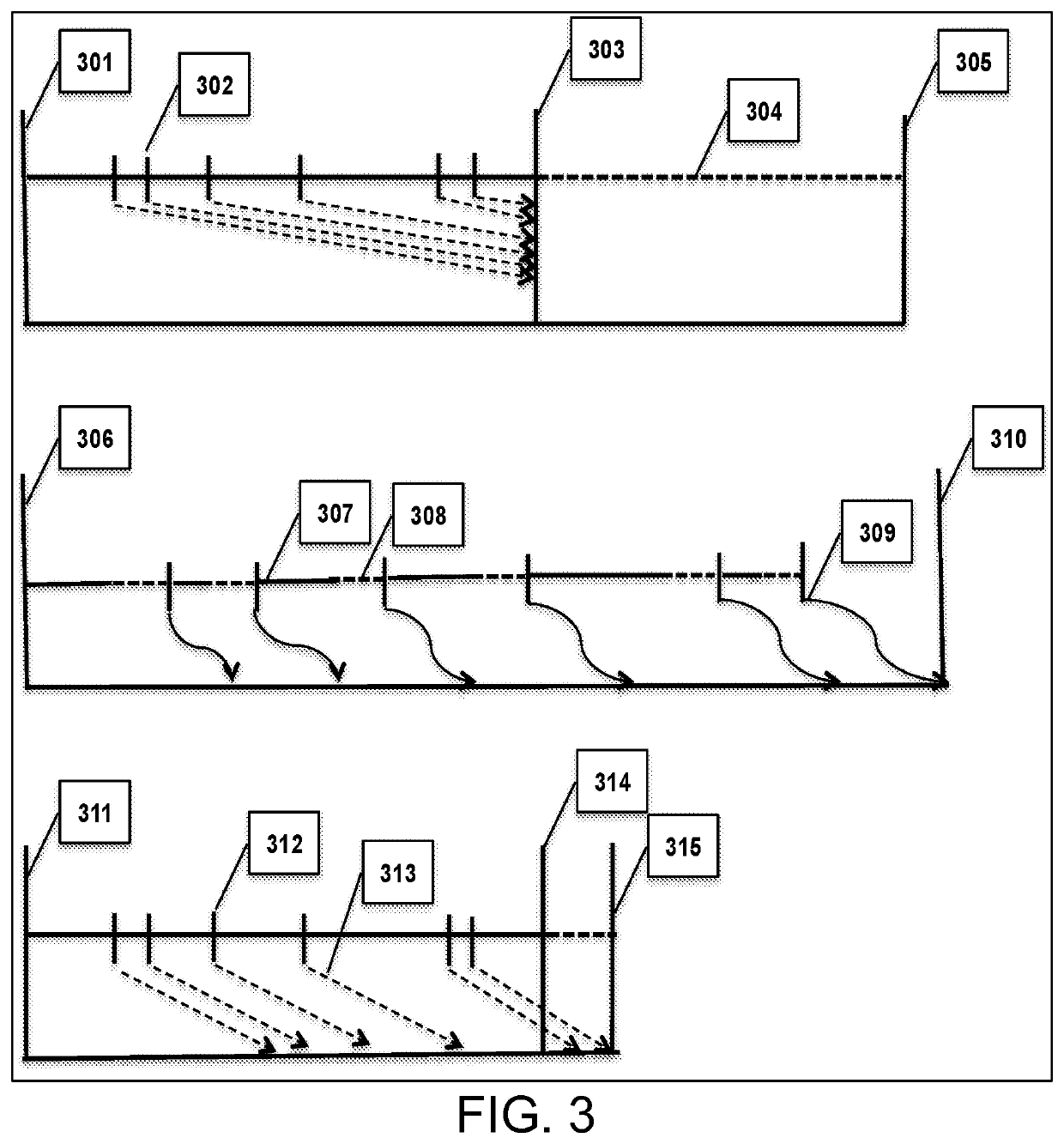

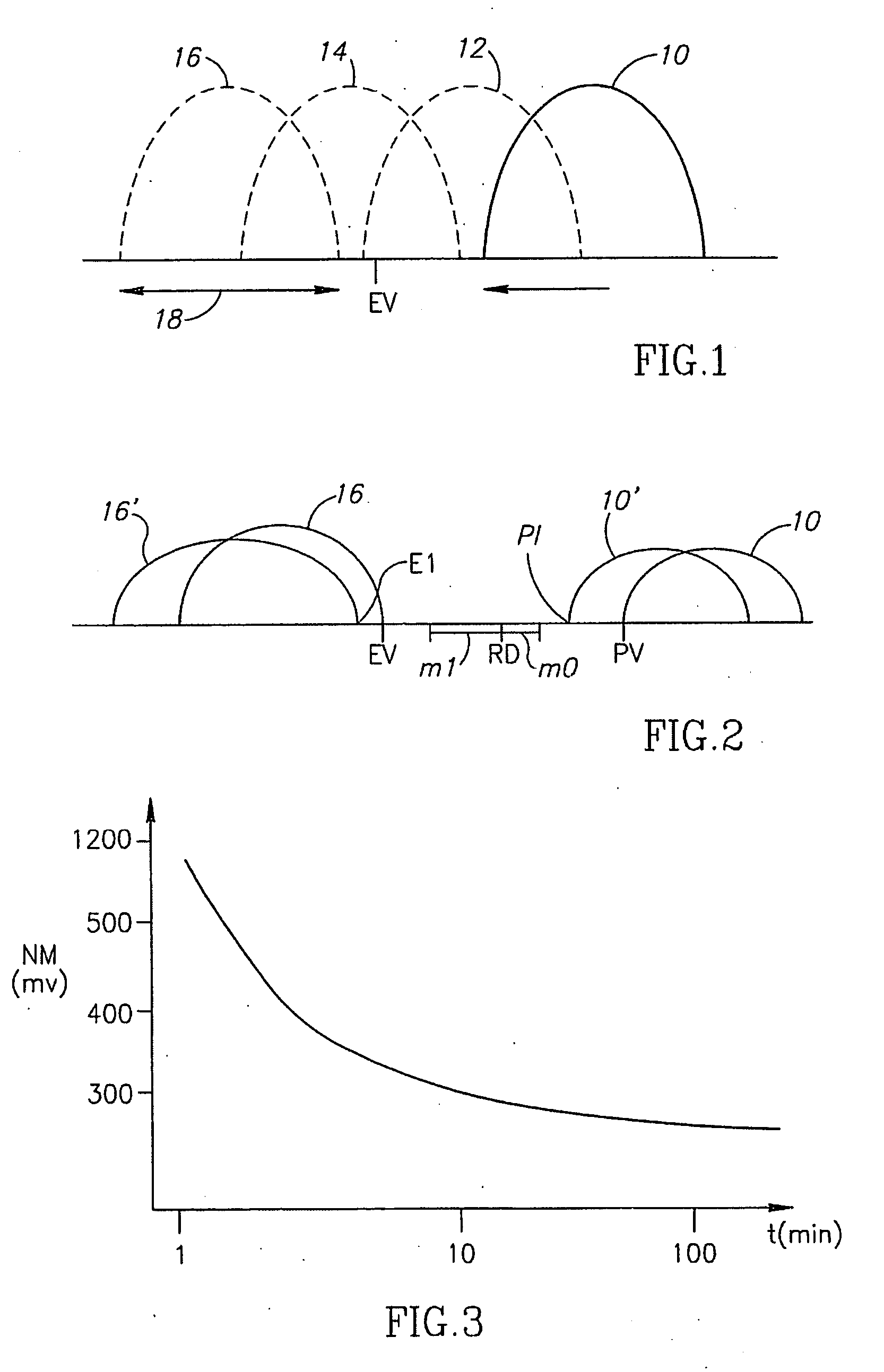

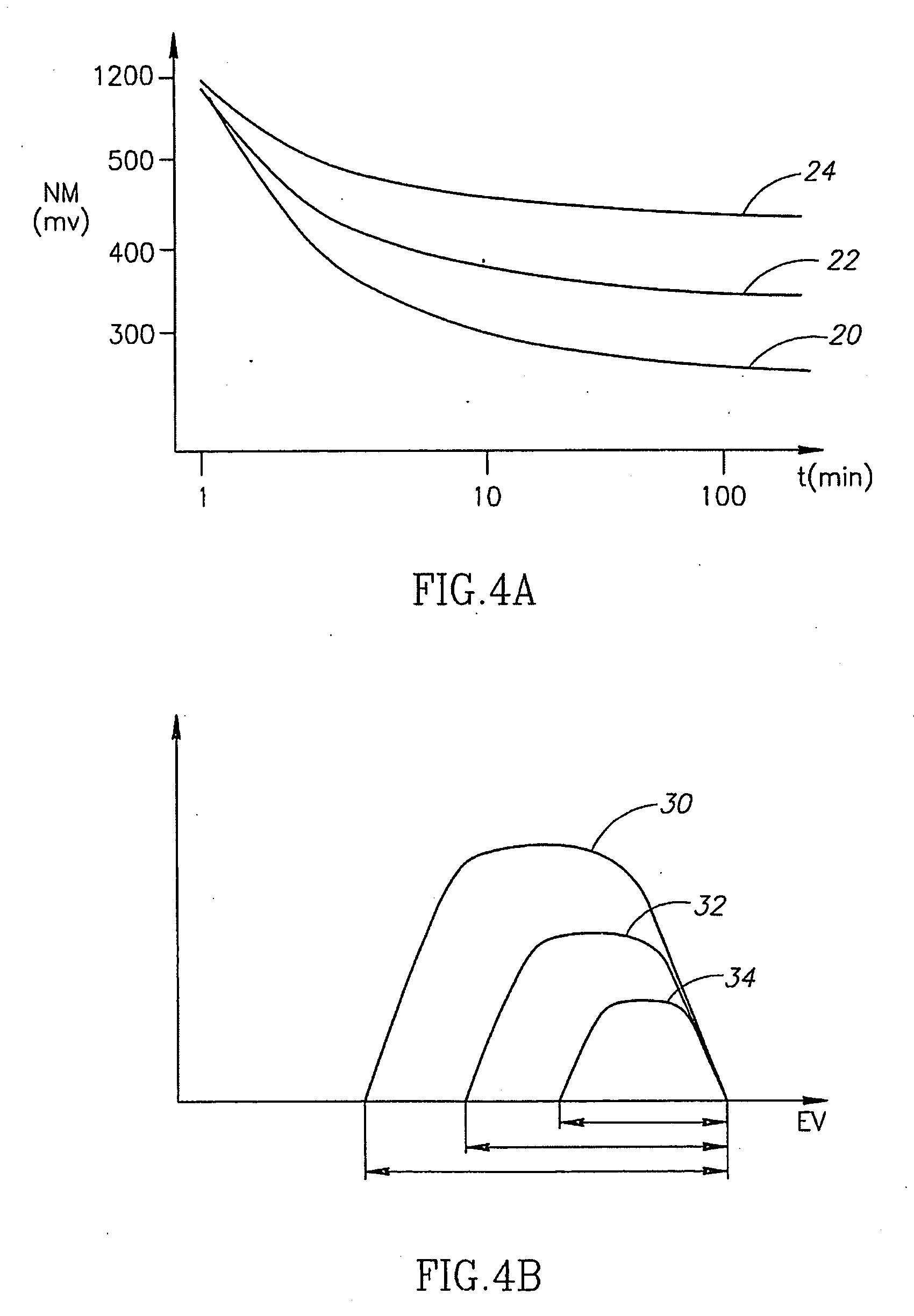

Method of erasing non-volatile memory cells

Owner:SAIFUN SEMICON

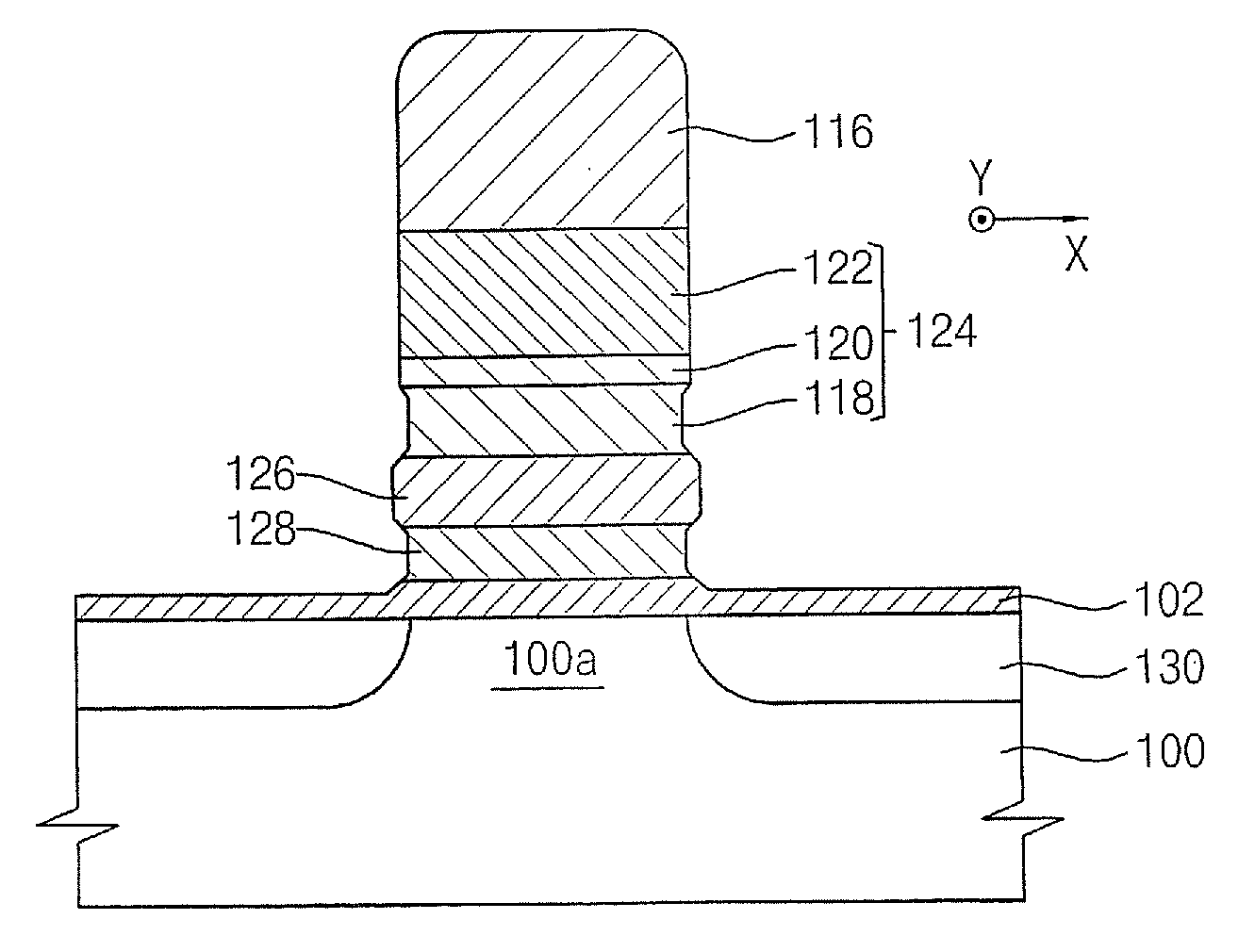

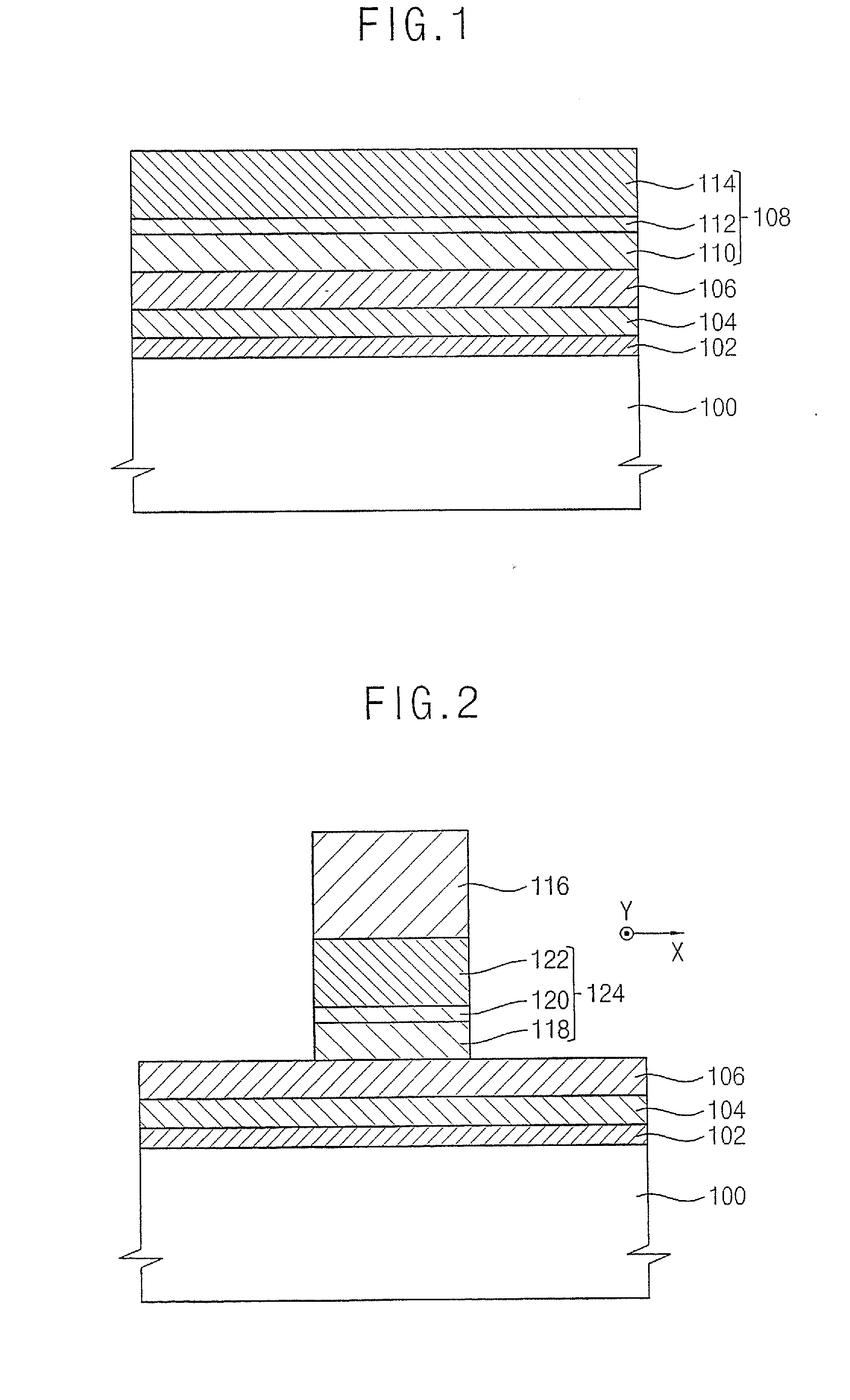

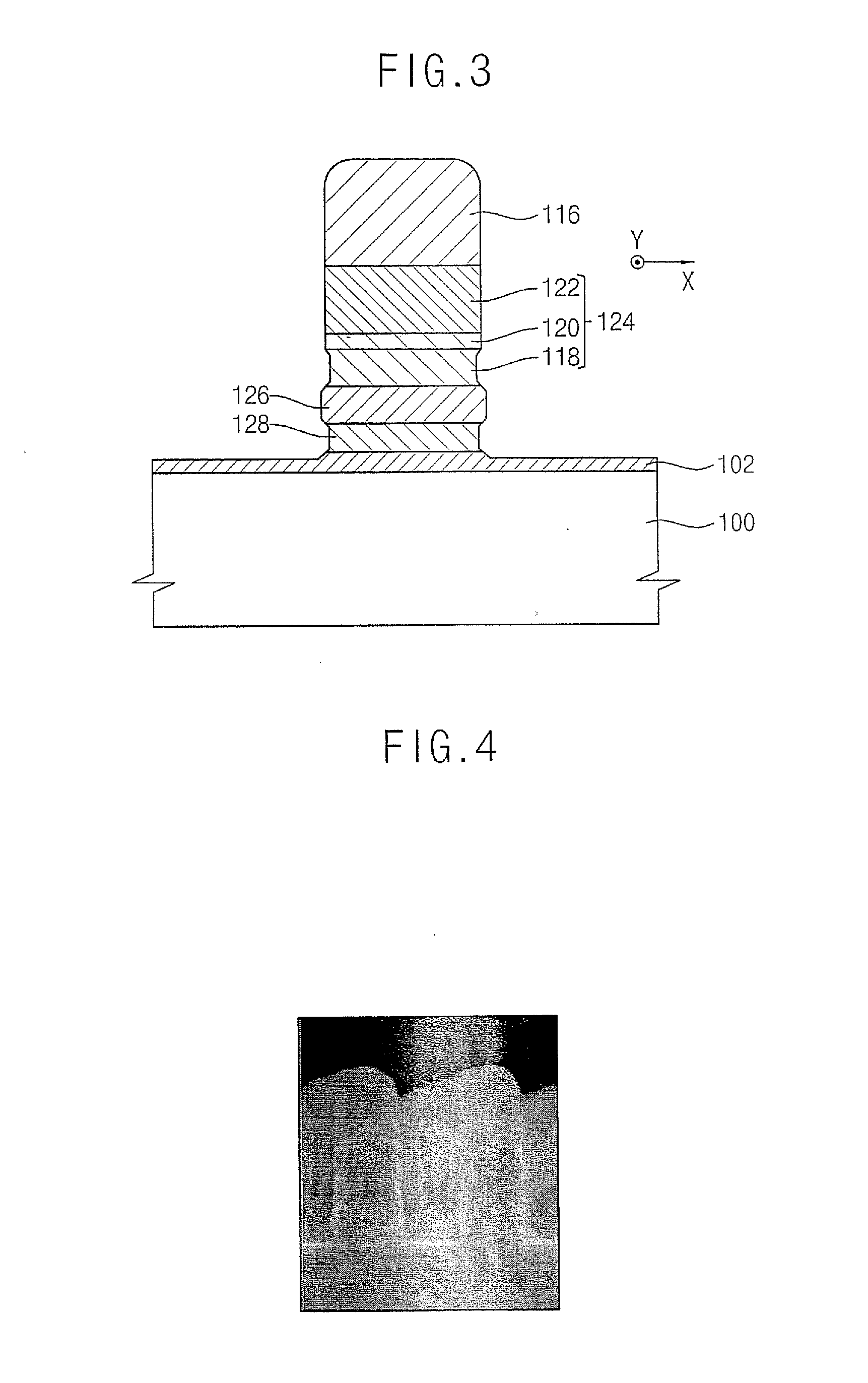

Methods of Manufacturing Non-Volatile Memory Devices Including Charge-Trapping Layers

InactiveUS20080188049A1Increase etch rateSurgerySemiconductor/solid-state device manufacturingTrappingAqueous solution

Owner:SAMSUNG ELECTRONICS CO LTD

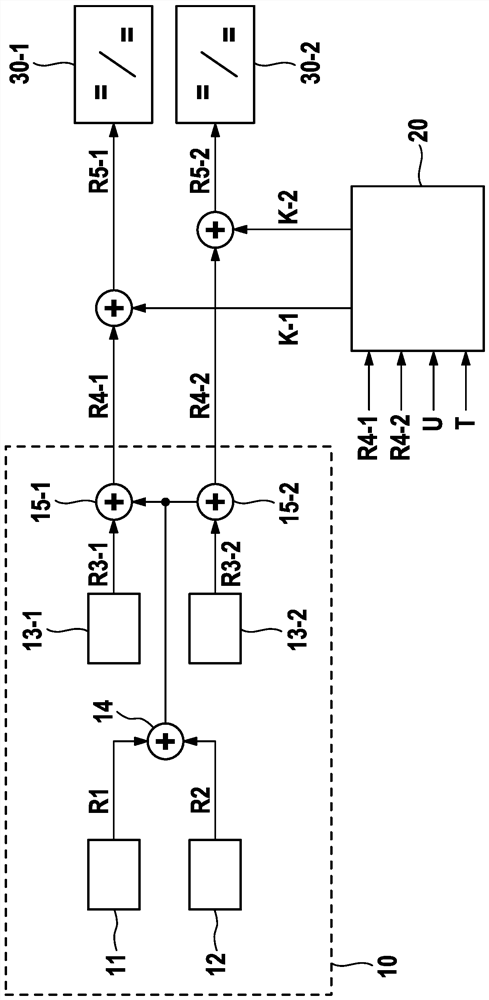

Regulating device for dc-dc converter and method for regulating dc-dc converter

PendingCN114402517AConsider aging effectsRandom combinationDc-dc conversionElectric variable regulationConvertersEngineering

Owner:ROBERT BOSCH GMBH

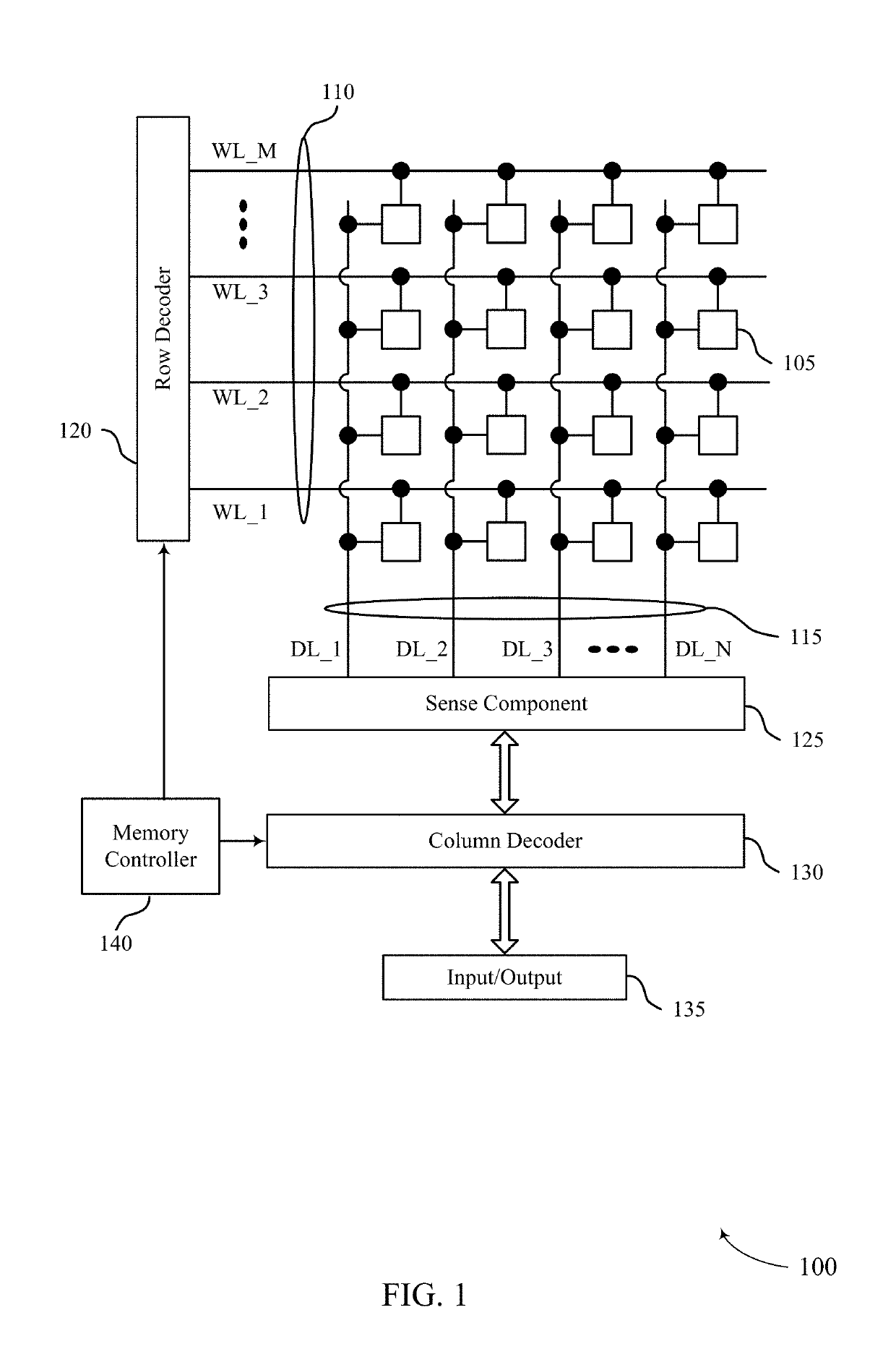

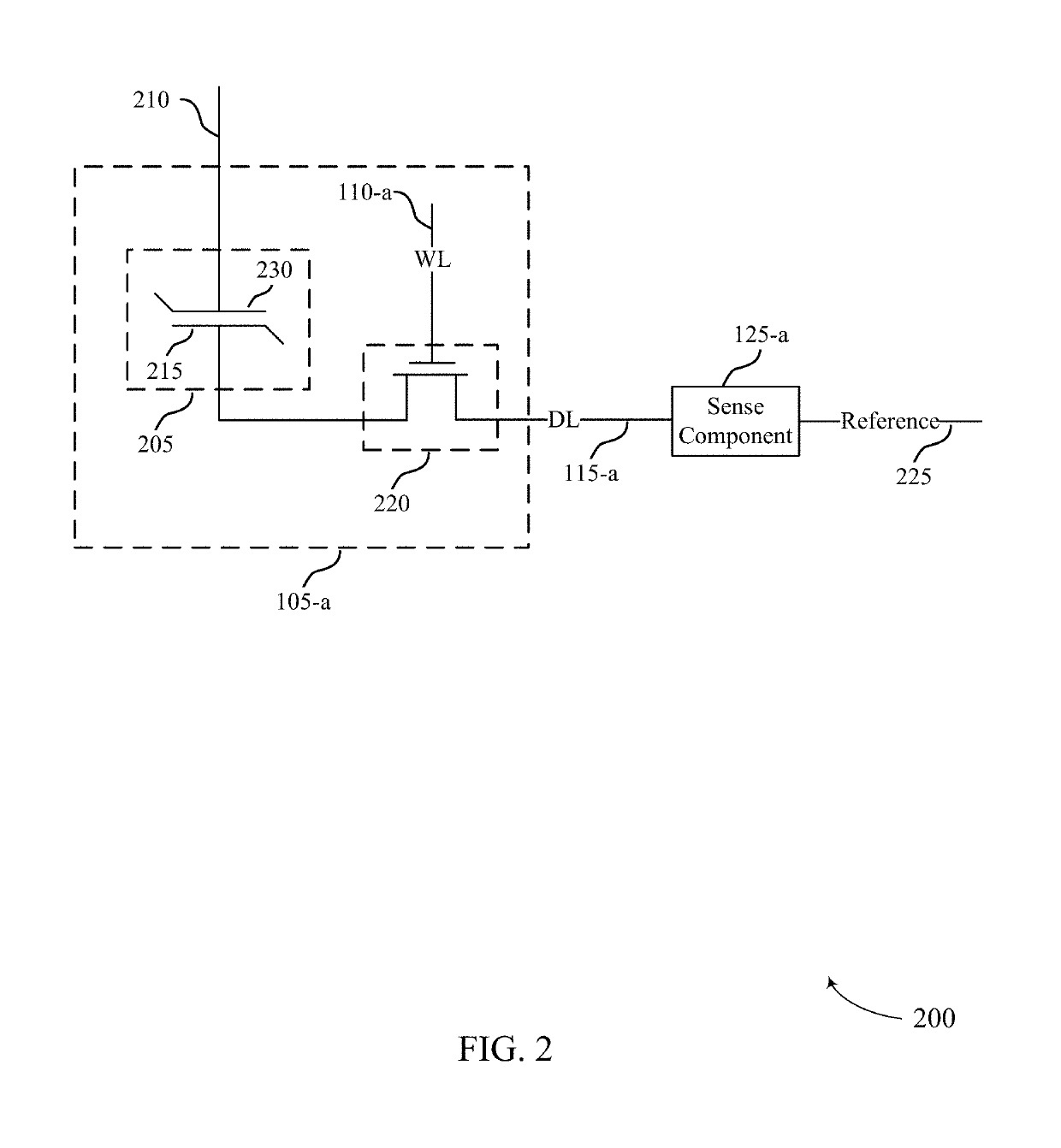

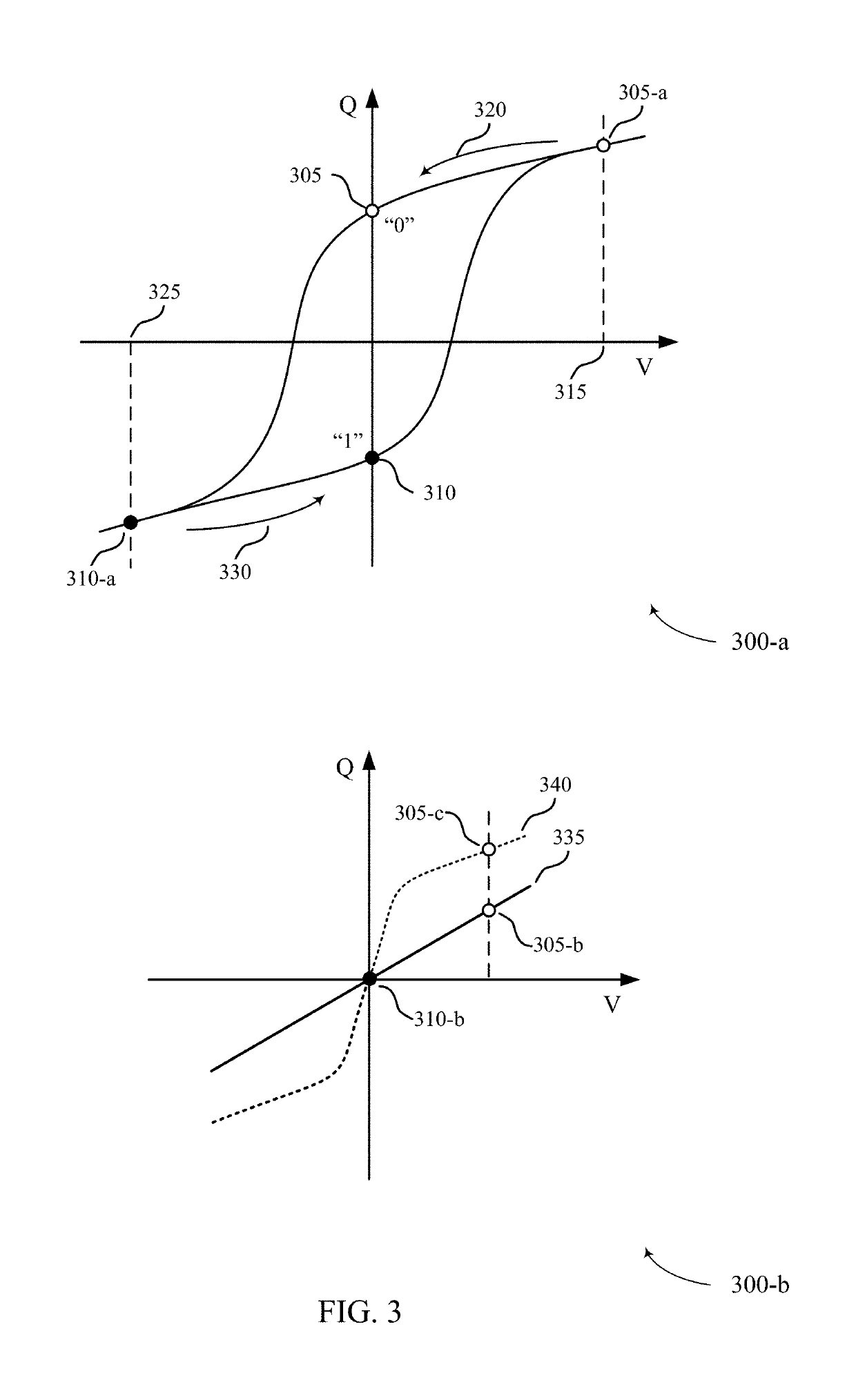

Hybrid memory device using different types of capacitors

Owner:MICRON TECH INC

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap