Manufacturing method of film transistor matrix substrate

A technology of a thin film transistor and a manufacturing method, which is applied in the field of manufacturing a thin film transistor matrix substrate, can solve the problems of difficult control and difficulty in the actual process, and achieve the effects of reducing photocurrent generation, reducing film thickness, and reducing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

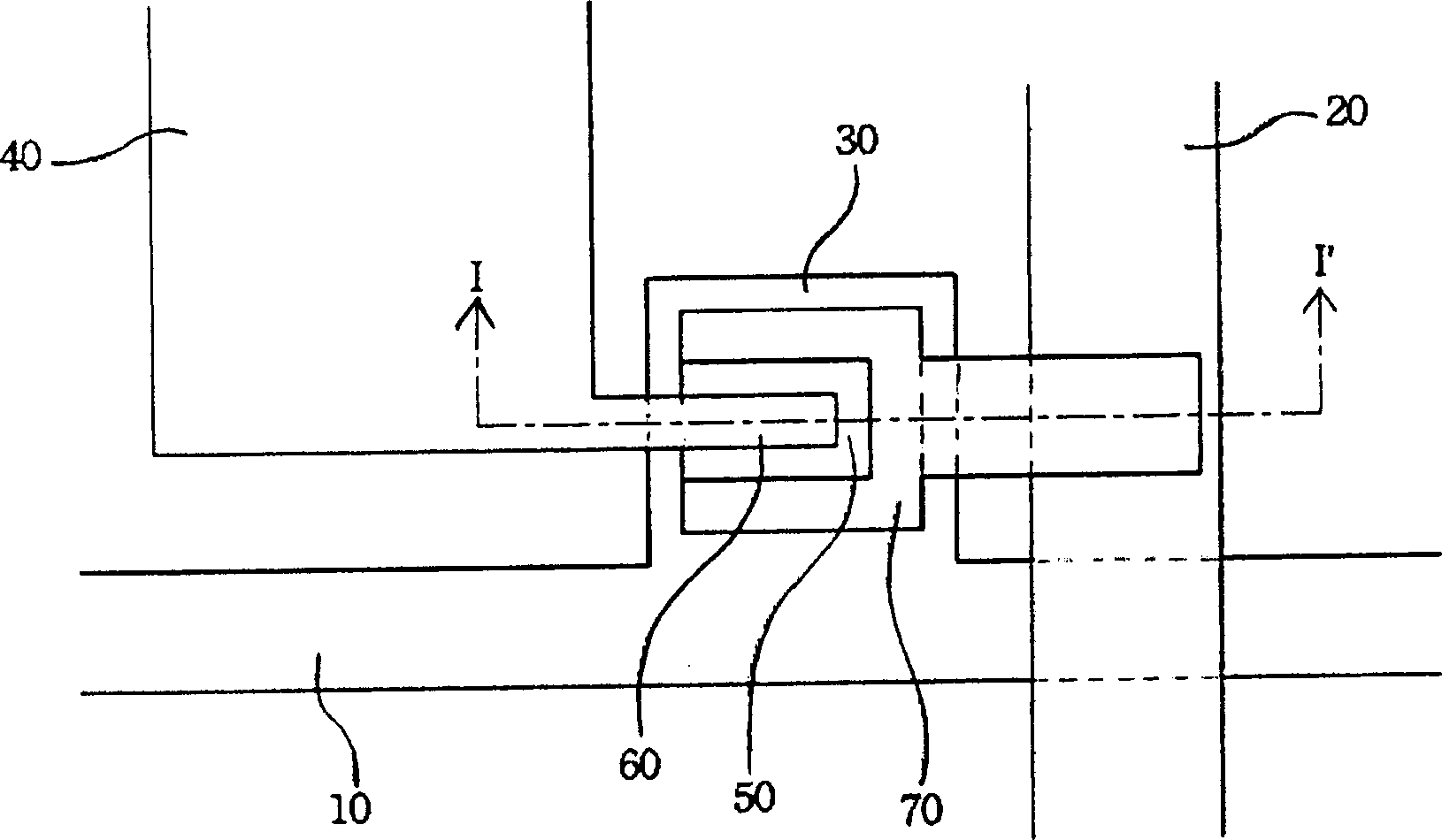

[0036] Please refer to image 3 , image 3 A schematic top view of the transistor array substrate (pixel unit structure) formed by a four-pass mask process according to a preferred embodiment of the present invention is shown. The transistor array substrate includes gate lines (scanning lines) 10 , signal lines or signal electrodes (data lines) 20 , gate electrodes 30 , pixel electrodes 40 , island-shaped semiconductors 50 , and source / drain electrodes 60 and 70 .

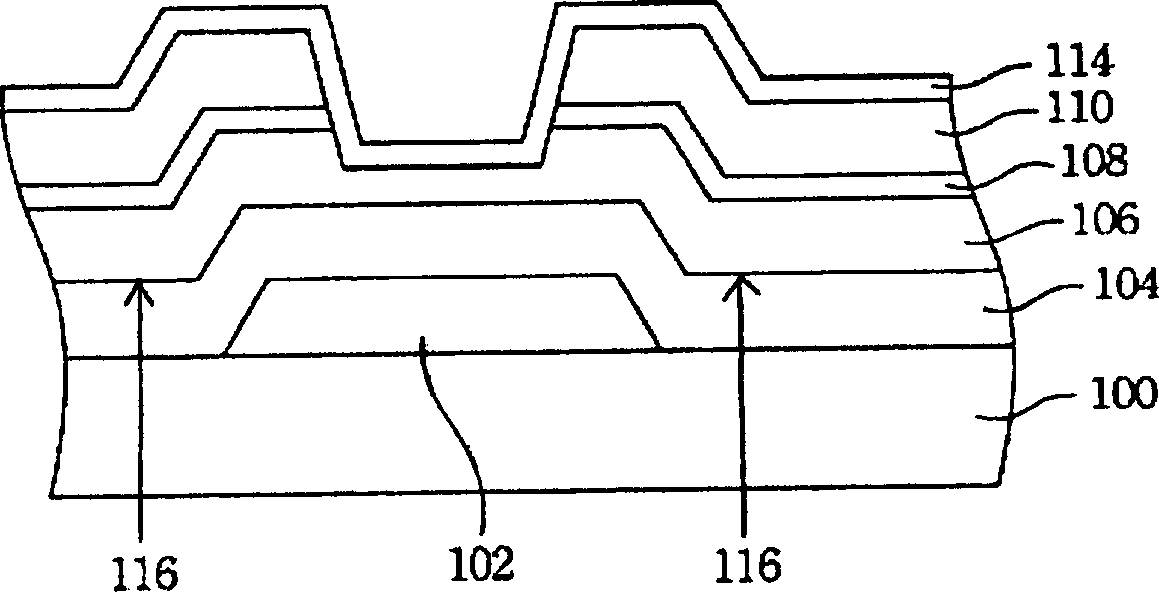

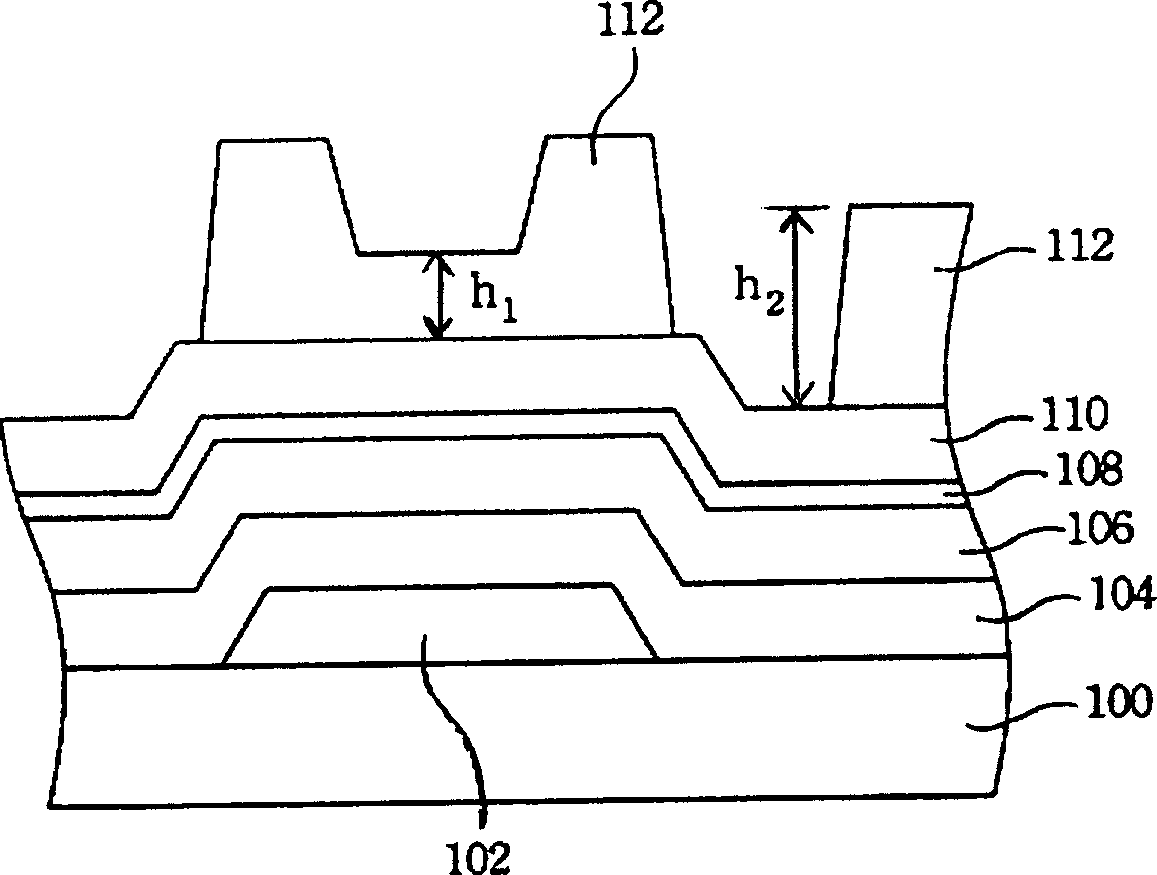

[0037] Please refer to Figure 4A to Figure 4D , Figure 4A to Figure 4D along image 3 As shown by the I-I' section line in the figure, it is a cross-sectional schematic diagram of the manufacturing process of the transistor array substrate formed by the four-pass mask process. Please refer to Figure 4A , on the transparent substrate 200, a conductive layer is defined by a mask process to form gate electrodes 30 and gate lines (scanning lines) (not shown). The transparent substrate 200 may be, for example, a

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap