Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

9 results about "Semiconductor technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

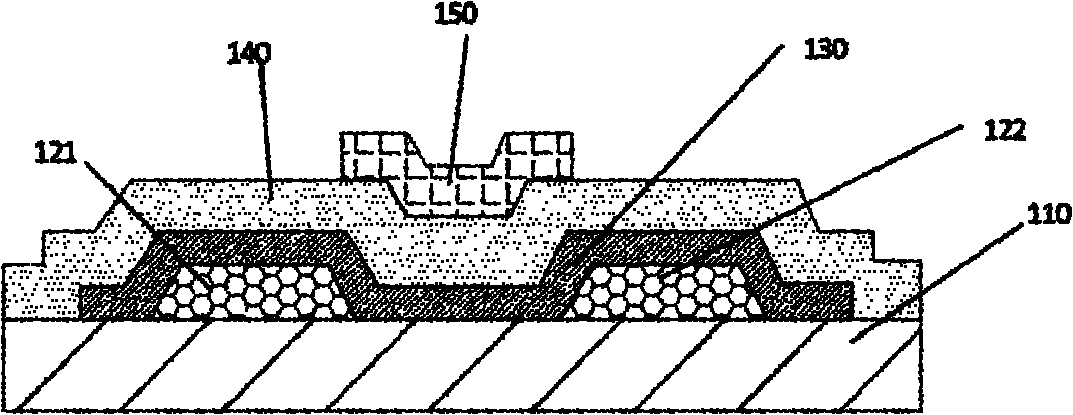

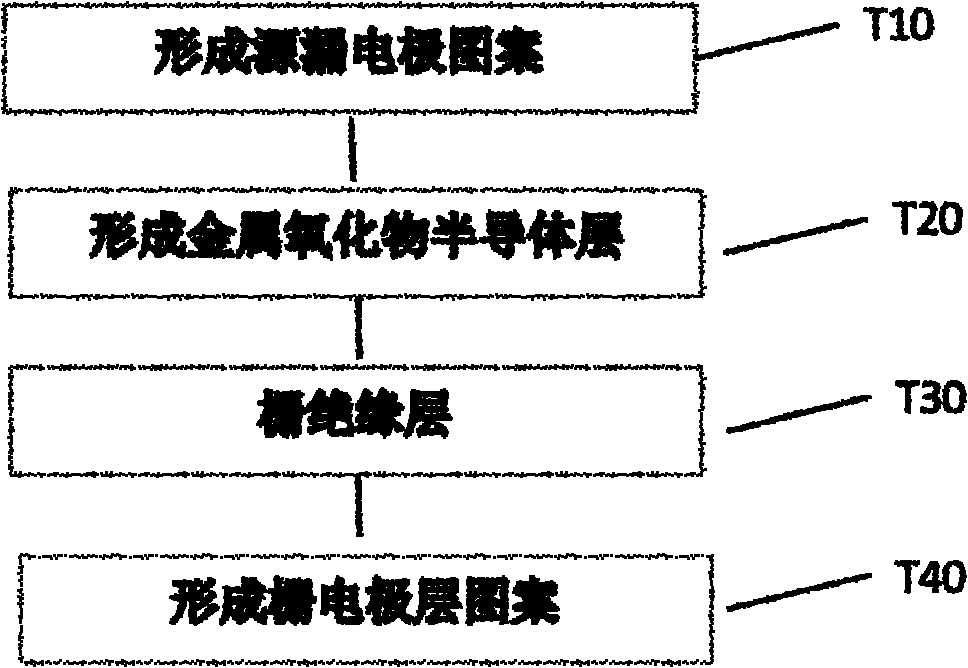

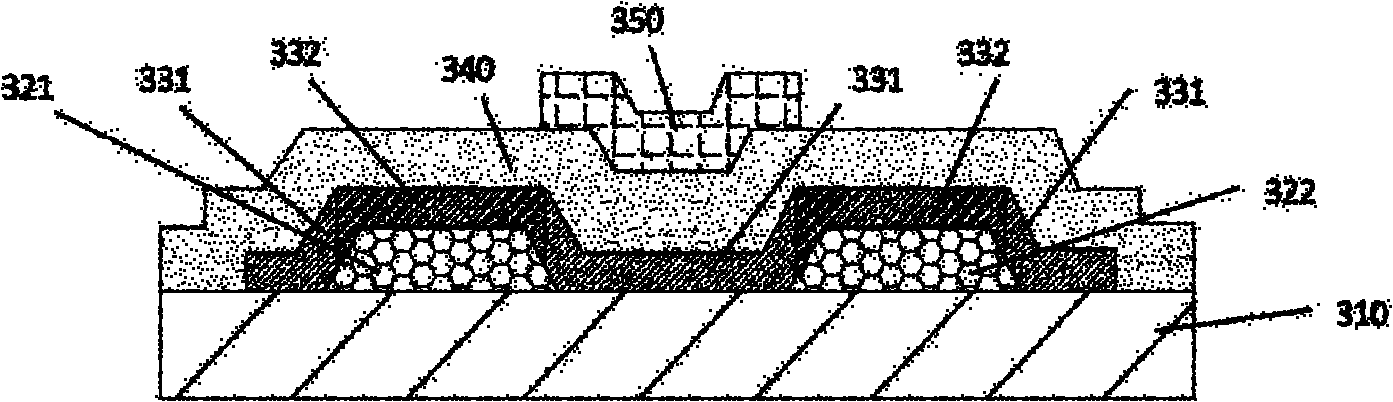

Preparation method of top gate metal oxide thin film transistor (TFT)

InactiveCN102157564ASolve the technical problem of insufficient chargingIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingEtchingElectrical conductor

Owner:SHANGHAI JIAO TONG UNIV

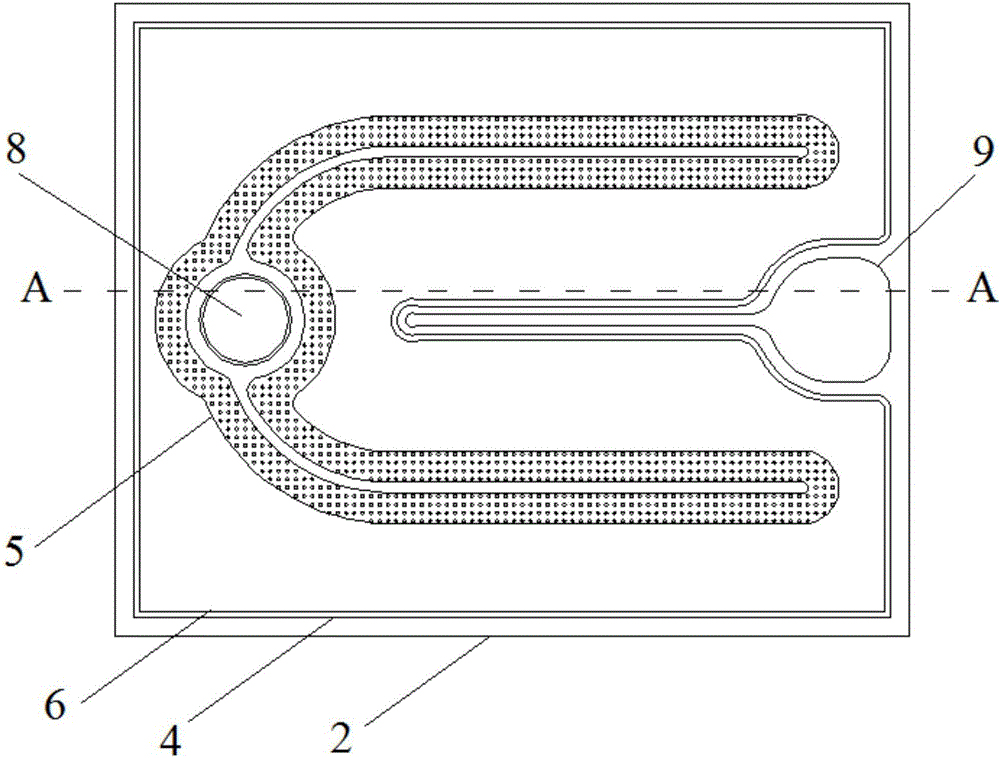

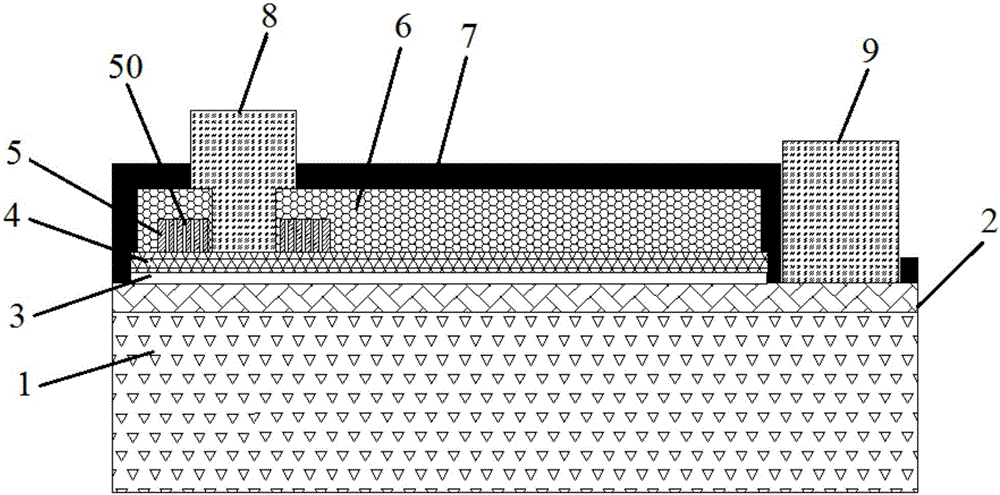

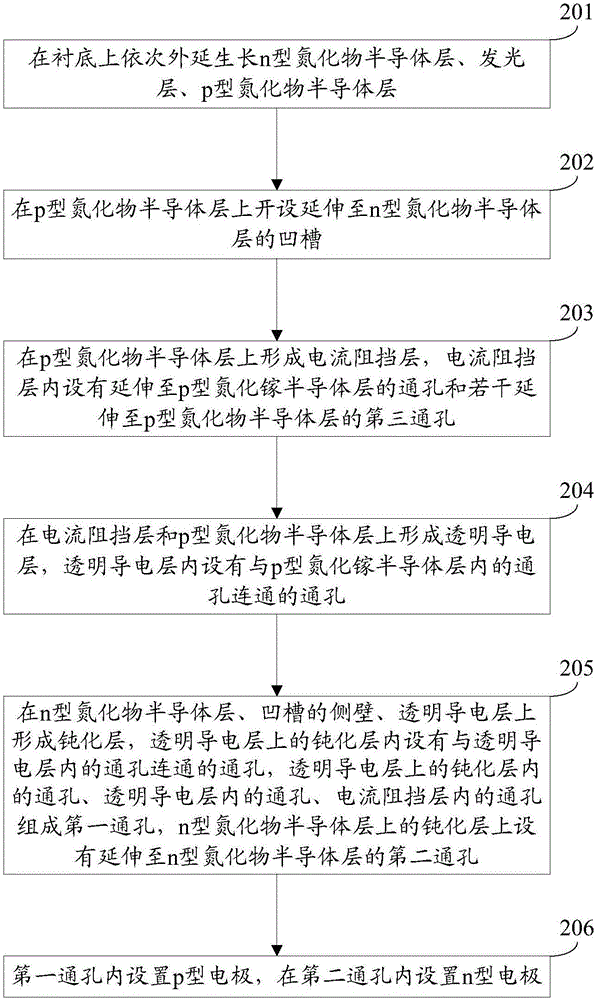

LED chip and manufacturing method therefor

ActiveCN106784218AImprove light extraction efficiencyImprove luminous brightnessSemiconductor devicesLight-emitting diodeSemiconductor technology

Owner:HC SEMITEK ZHEJIANG CO LTD

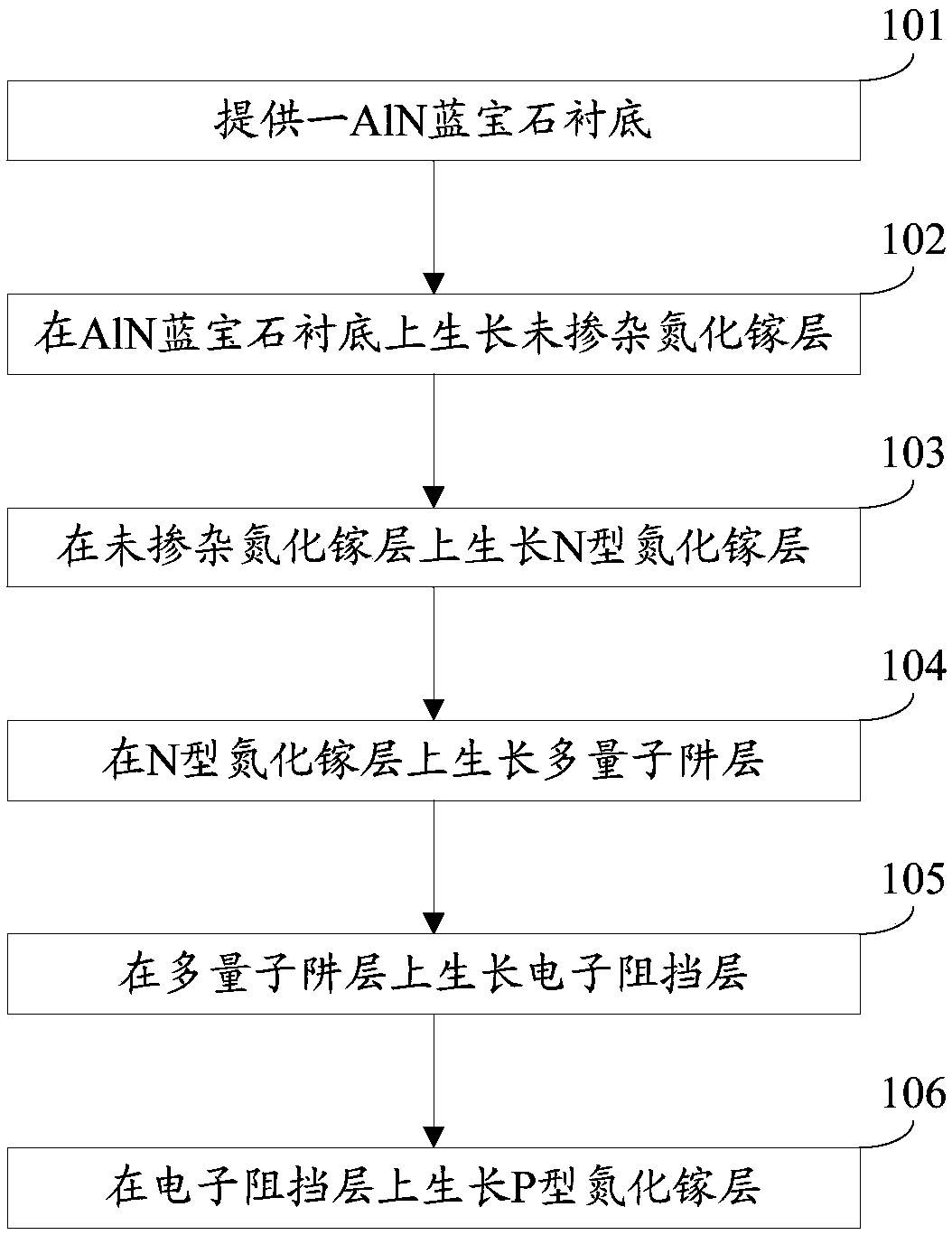

Preparation method of light emitting diode epitaxial wafer

Owner:HC SEMITEK SUZHOU

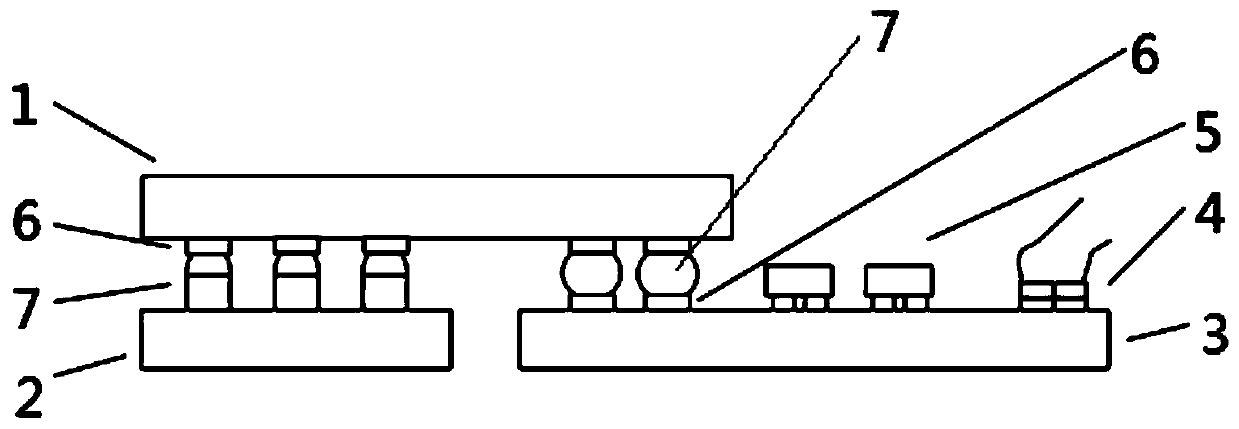

Test device and test method

ActiveCN112327128ACause damageGuaranteed sensitivityMeasurement instrument housingIndividual semiconductor device testingTest objectSemiconductor technology

The invention discloses a test device and a test method, relates to the technical field of semiconductors, and solves the problems of contact damage of a to-be-tested object and a probe and unstable contact of the to-be-tested object and the probe in the prior art. The device specifically comprises a test probe, a test socket, a support frame and a test component; the test probe is arranged in thetest socket, the lower end face of the to-be-tested object abuts against the upper end of the test probe installed in the test socket, and the lower end of the test probe is electrically connected with the test component through the test socket; the test probe comprises a cylindrical pipe, a positioning ring, a first column end, a spring, a second column end, a sleeve, a lead screw nut, a liquidstorage pipe, a piston, a funnel-shaped pipe, a plugging ring, a conductive fluid and a fixing sleeve. According to the invention, the to-be-tested object and the test probe are effectively protected,and the requirements of more accurate and more effective measurement are met.

Owner:FTDEVICE TECH (SUZHOU) CO LTD

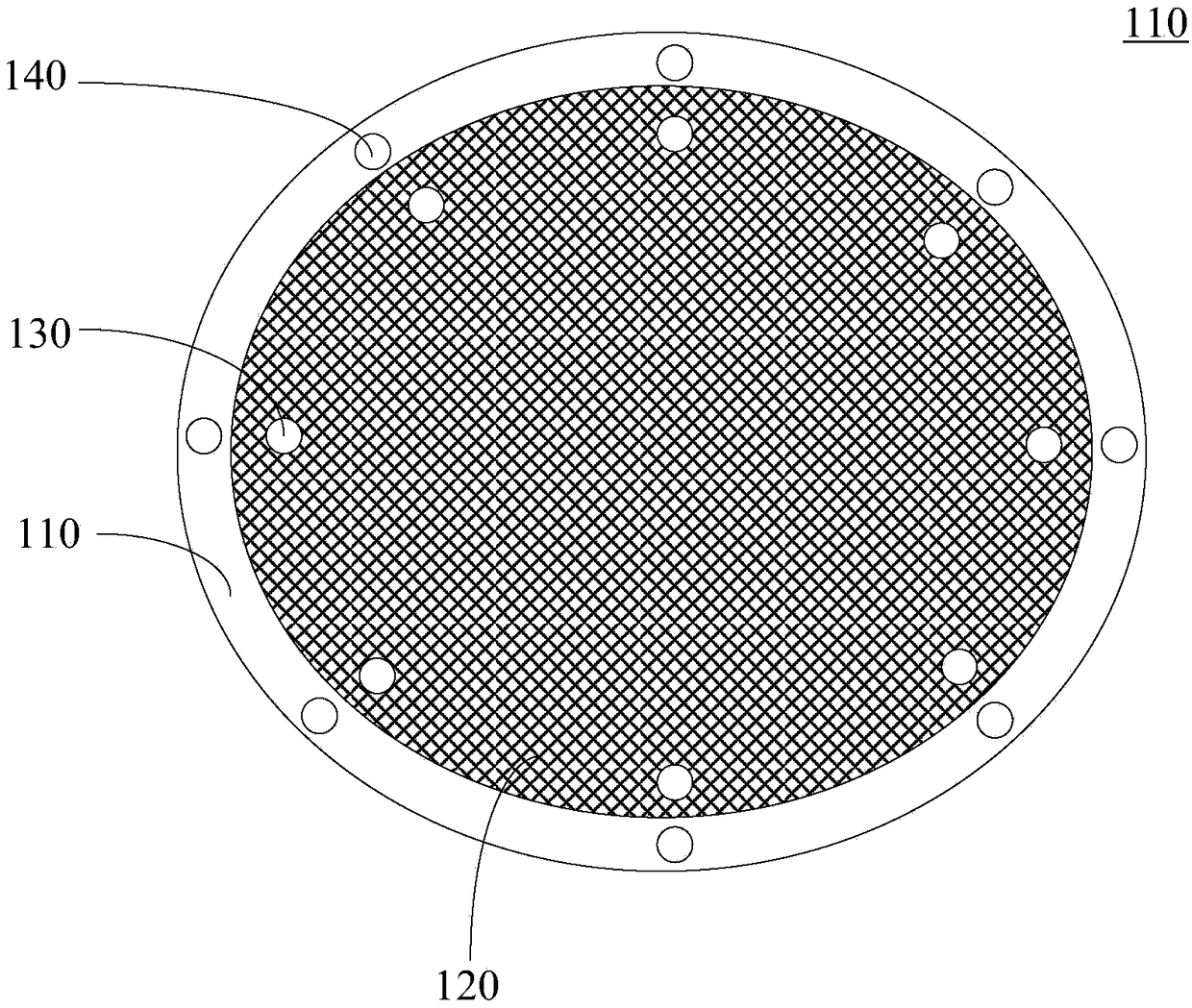

Spot measurement equipment of light emitting diode chip

Owner:HC SEMITEK ZHEJIANG CO LTD

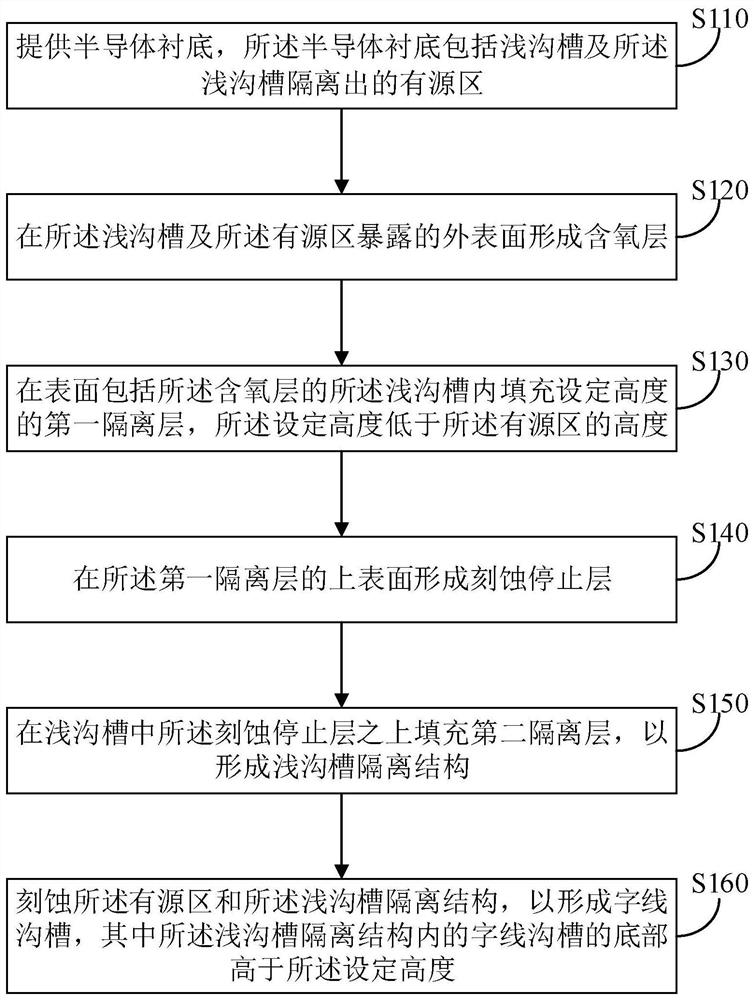

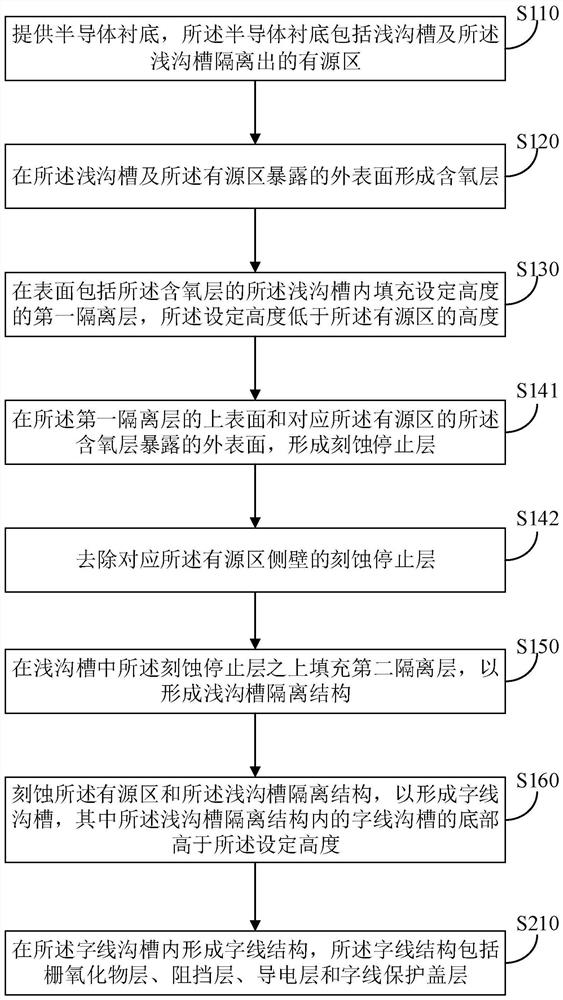

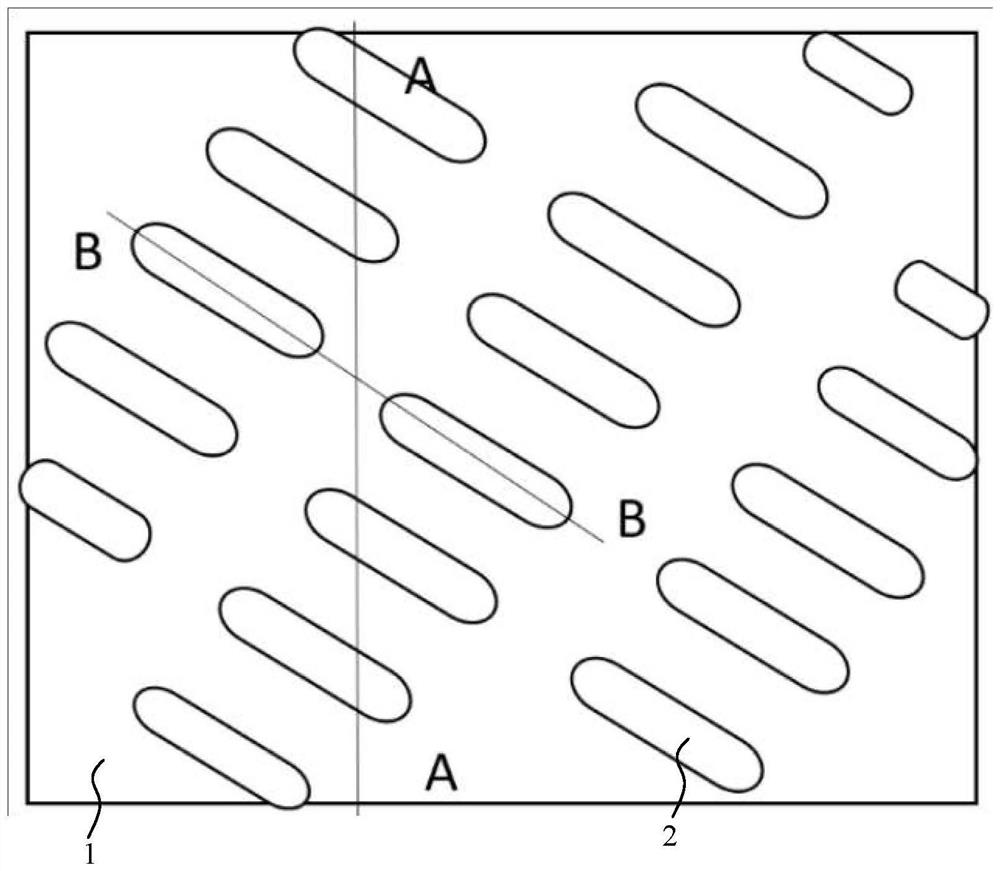

Preparation method of semiconductor device and semiconductor device

ActiveCN113990799AShorten the lengthIncrease parasitic capacitanceTransistorSemiconductor/solid-state device manufacturingDevice materialIsolation layer

Owner:CHANGXIN MEMORY TECH INC

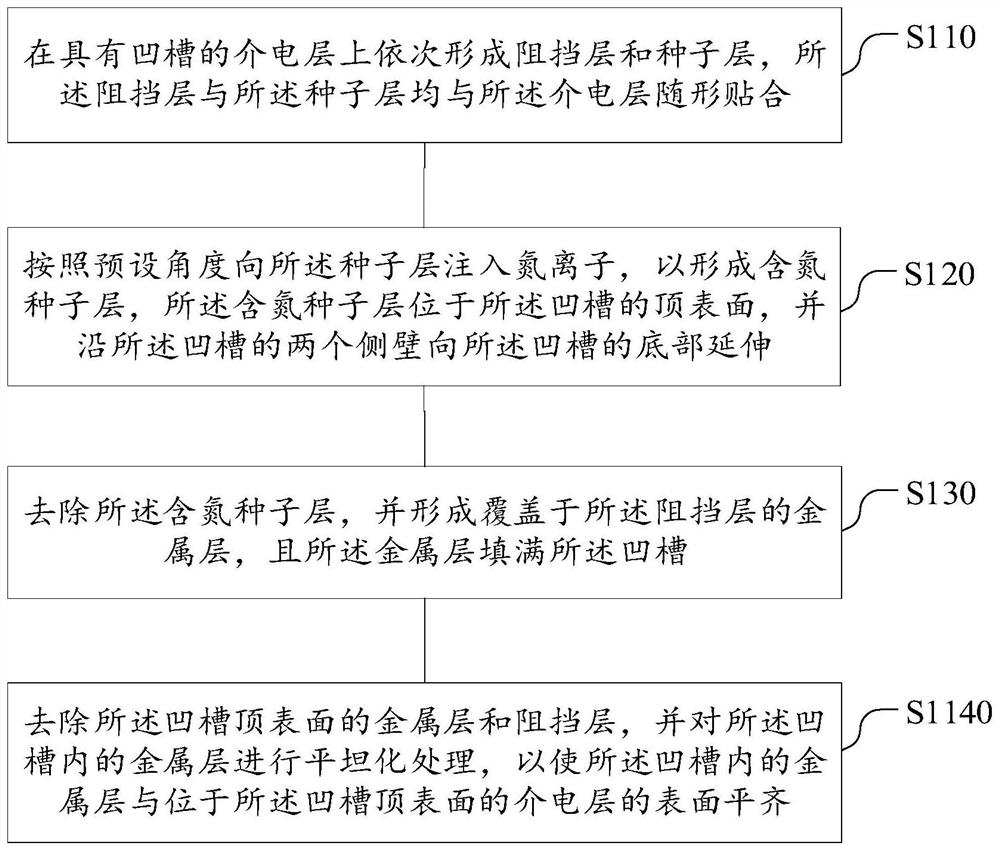

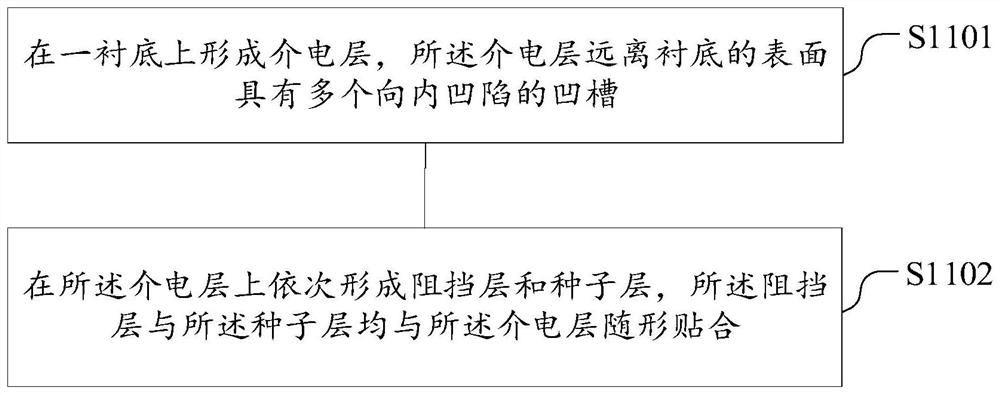

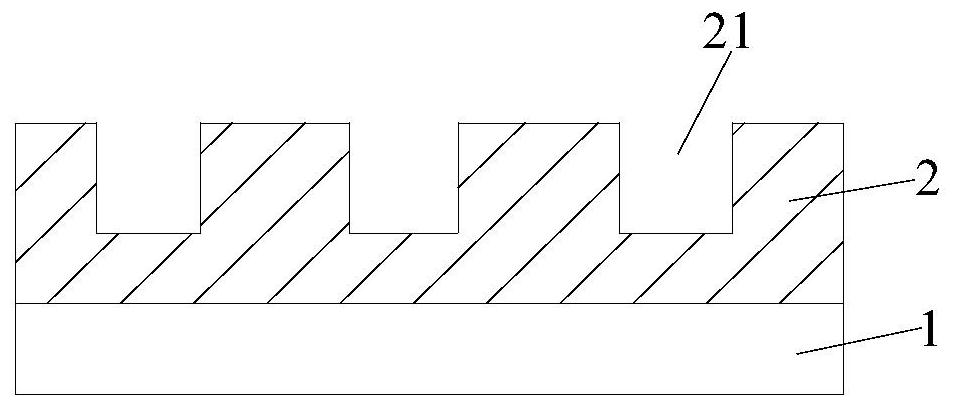

Semiconductor device, semiconductor structure and manufacturing method of interconnection structure

InactiveCN112530856AAvoid gatheringPrevent proliferationSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDevice material

Owner:CHANGXIN MEMORY TECH INC

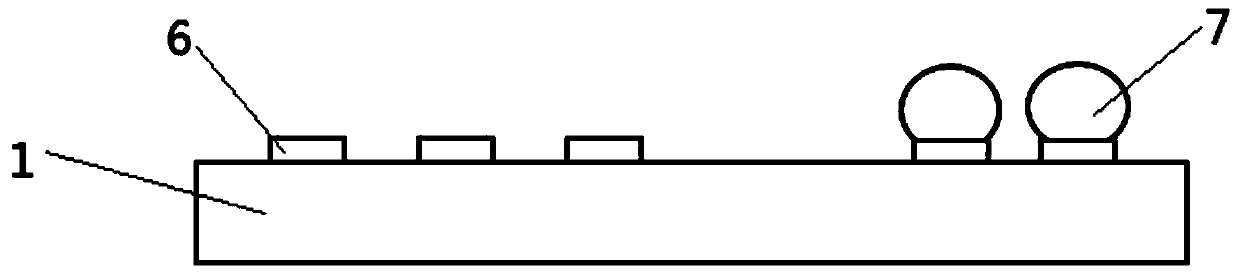

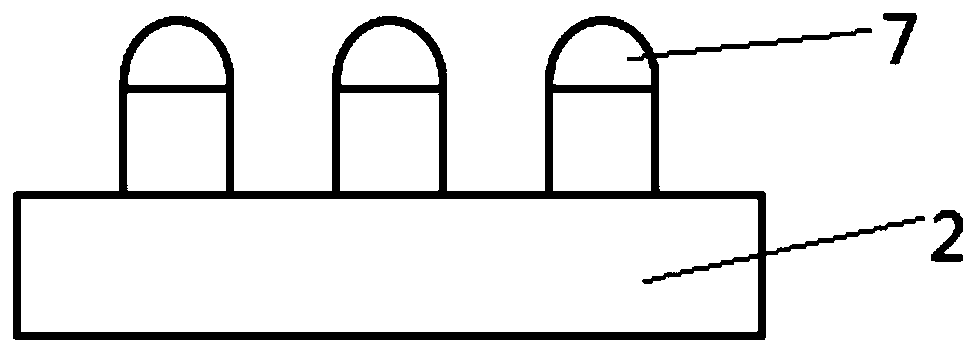

Packaging structure and packaging method

PendingCN111446227AReduce areaReduce packaging costsSemiconductor/solid-state device detailsSolid-state devicesEngineeringMechanical engineering

Owner:NAT CENT FOR ADVANCED PACKAGING

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap