Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7 results about "Etching rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In a simple sense, etch rate is rate of the peeling off (removing) a compound or changing it into its elemental form from a surface either by some physical or chemical method.

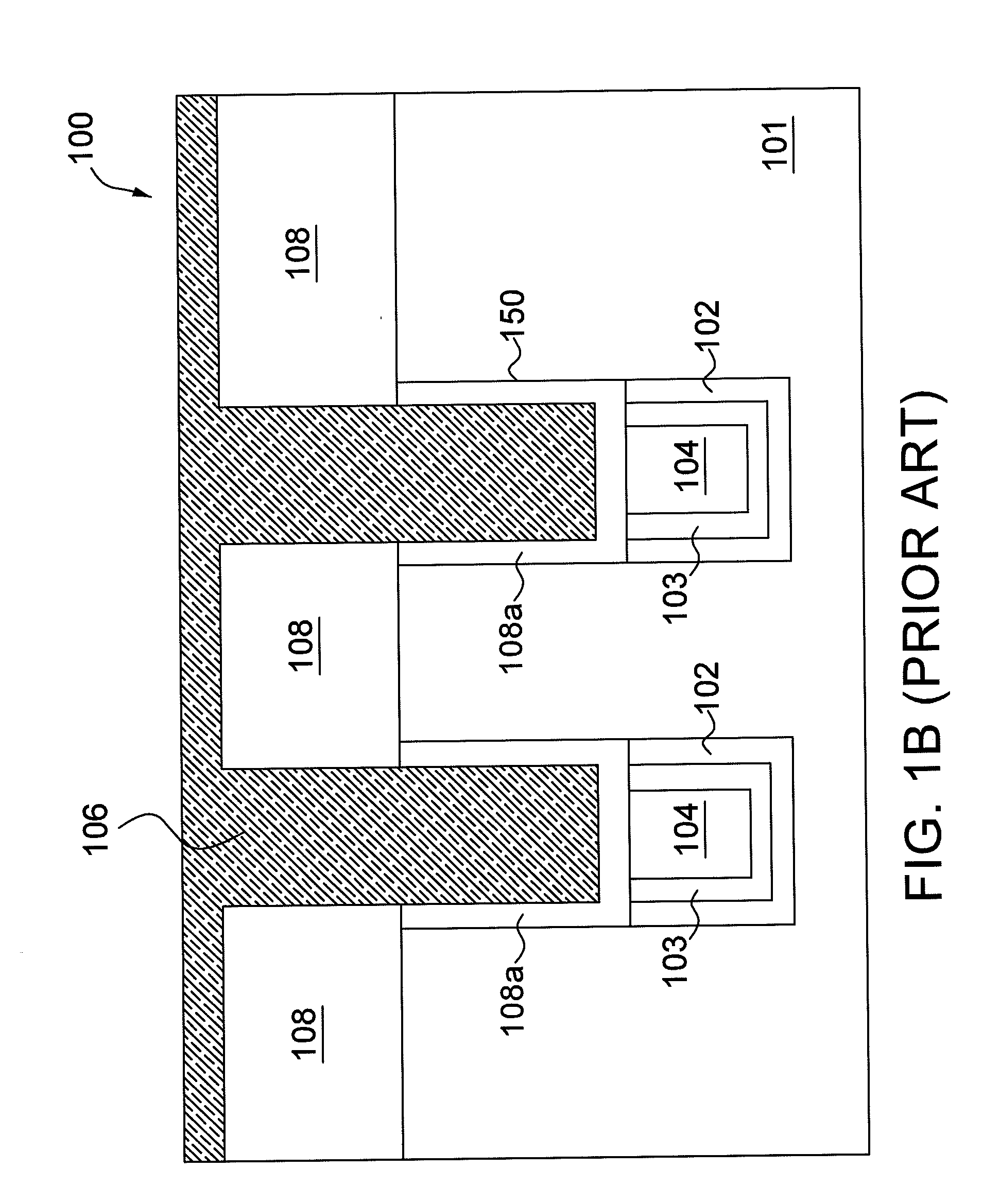

Method and apparatus for buried word line formation

ActiveUS20120039104A1Solid-state devicesSemiconductor/solid-state device manufacturingEtching rateIntegrated circuit

Owner:MICRON TECH INC

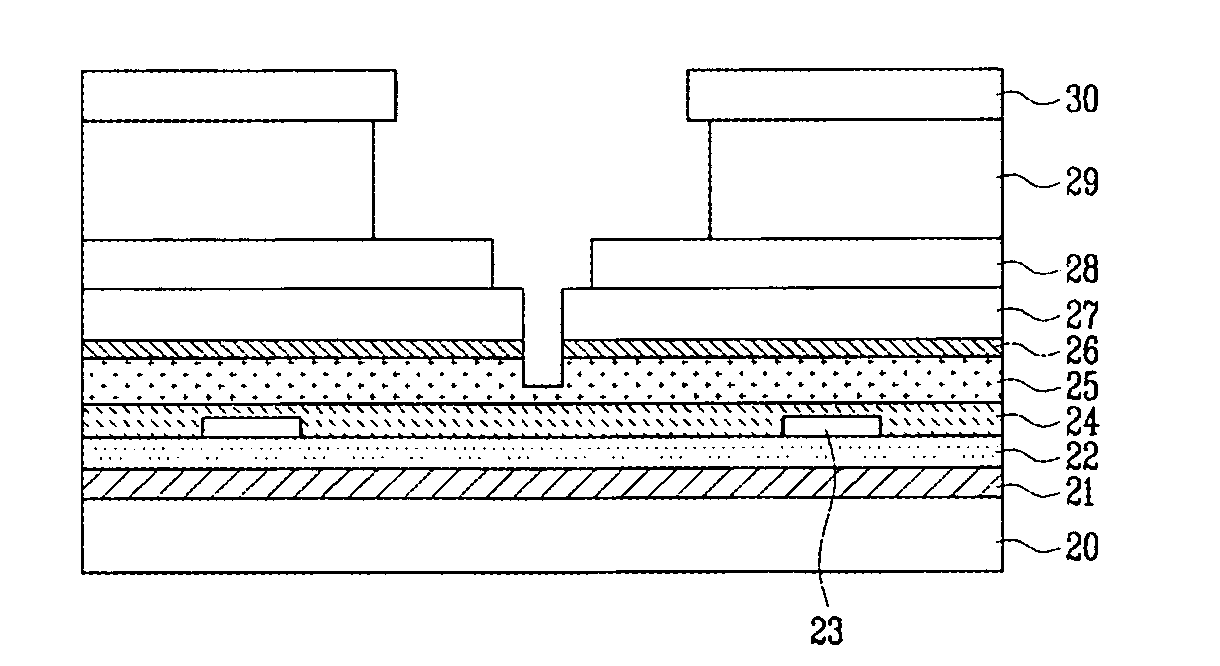

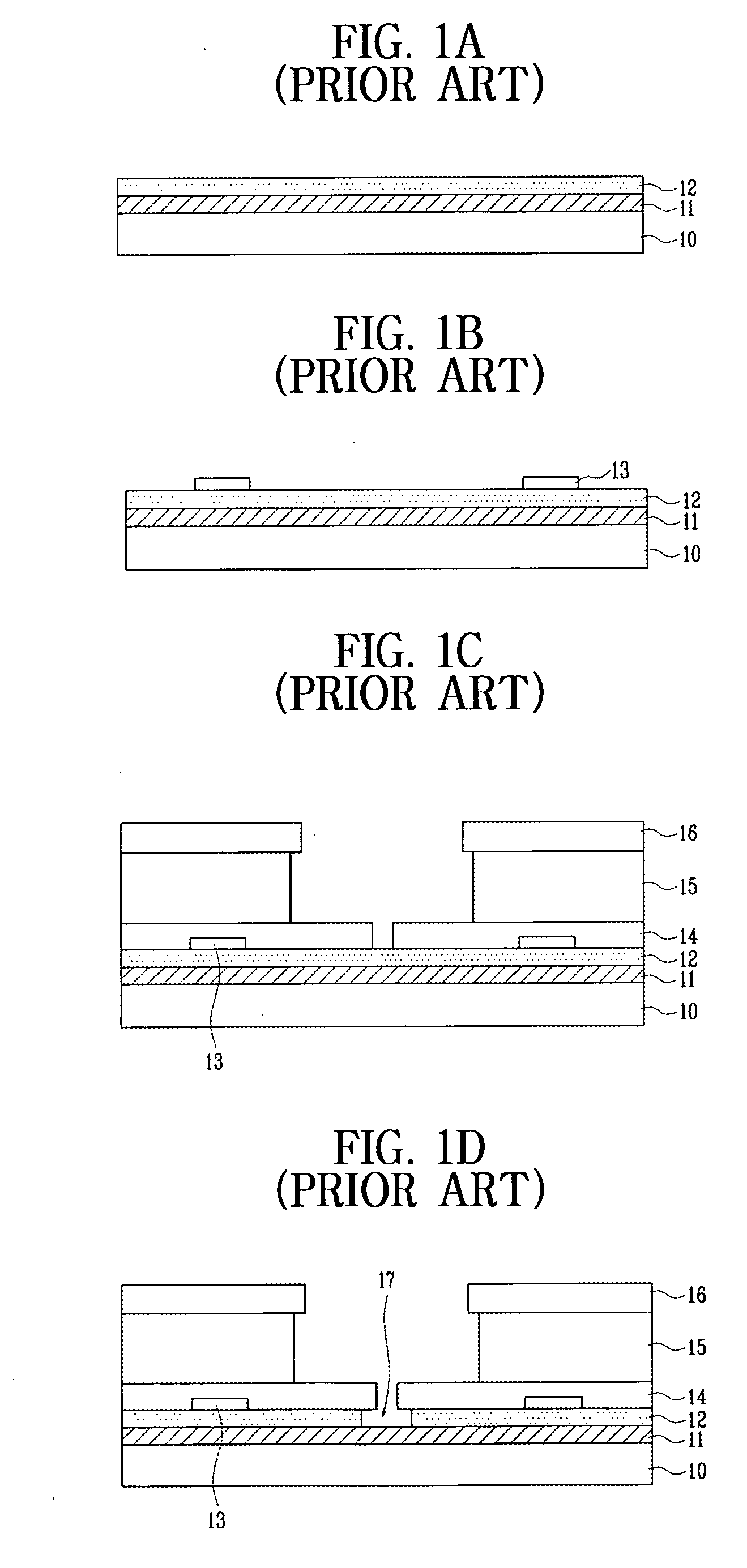

Field effect transistor and method for manufacturing the same

ActiveUS20070099368A1Different etch rateTransistorSemiconductor/solid-state device manufacturingParasitic capacitanceField-effect transistor

Owner:ELECTRONICS & TELECOMM RES INST

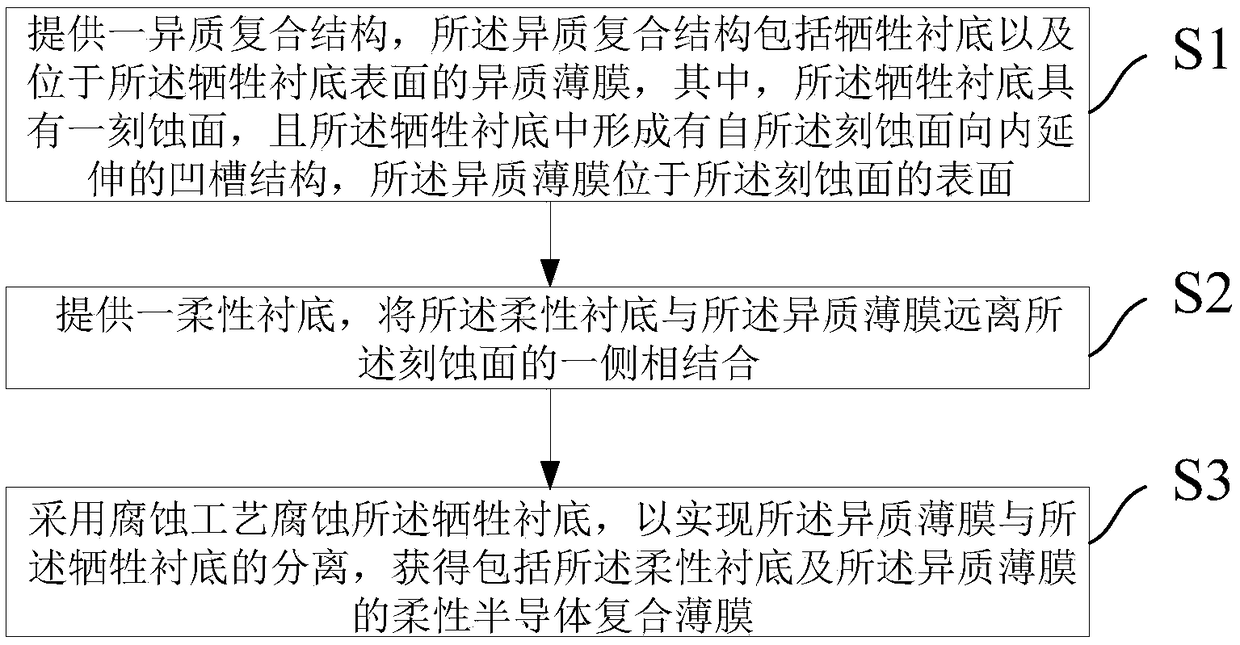

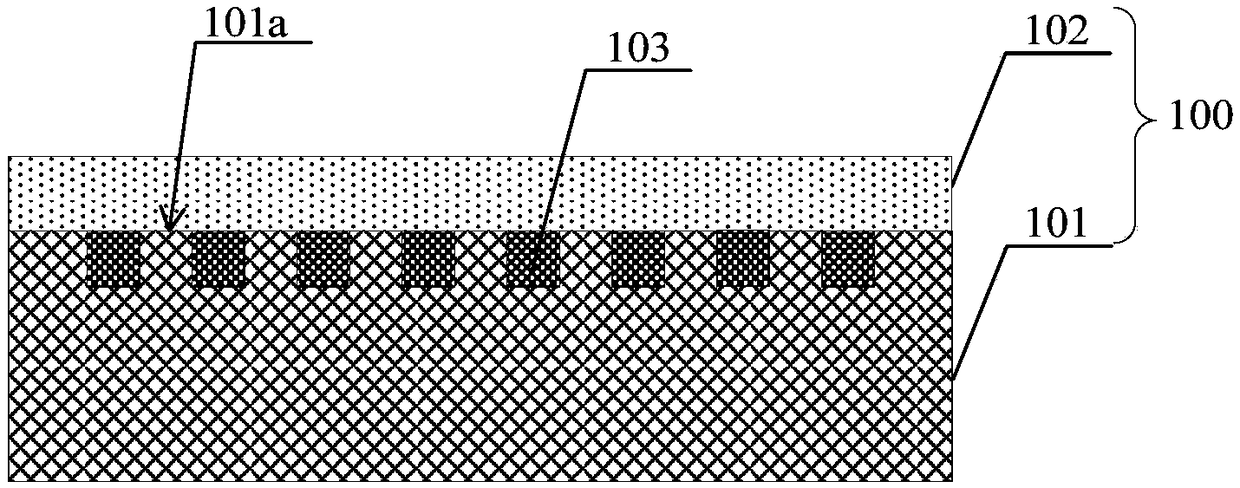

Flexible semiconductor composite film and preparation method thereof

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

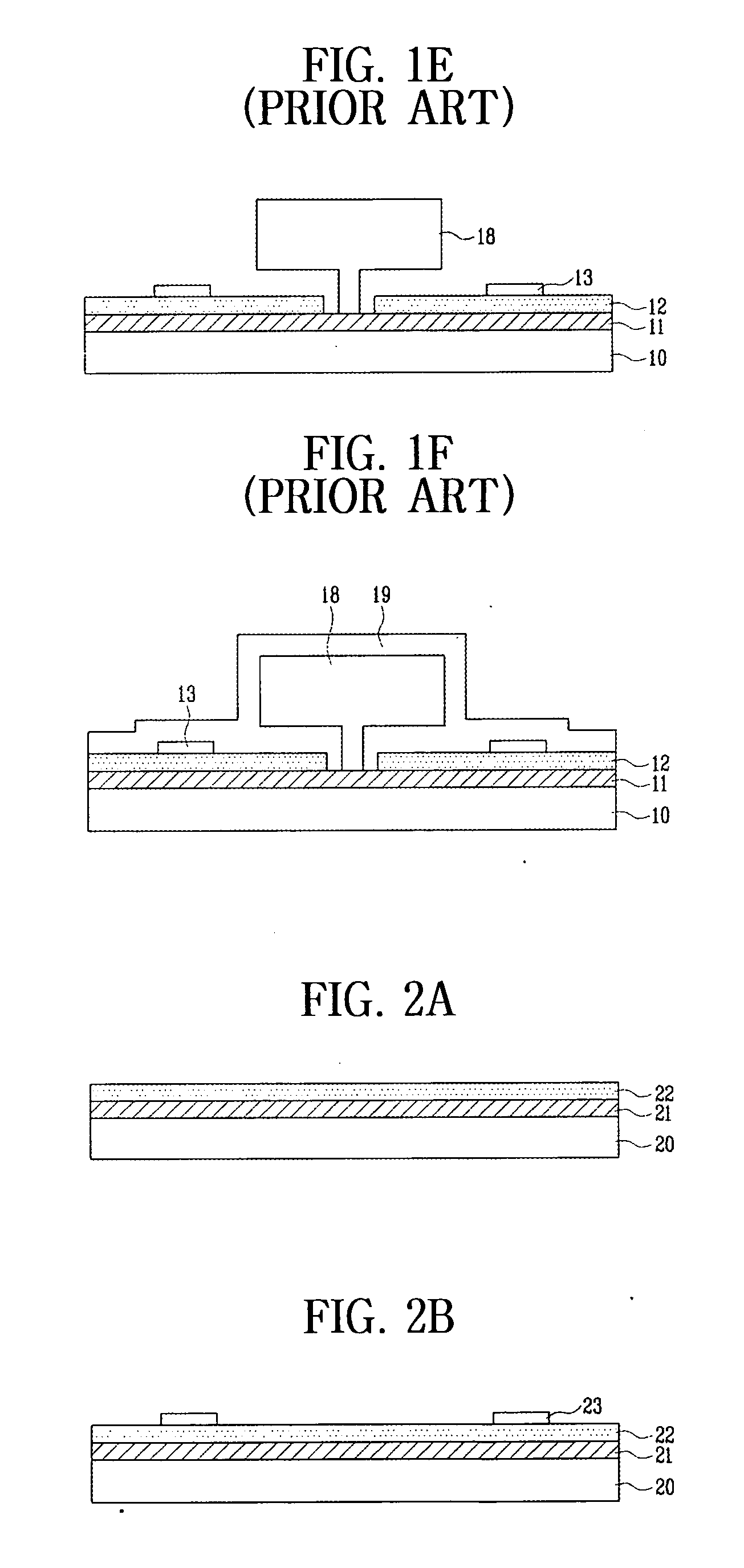

Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method

InactiveCN104862702ADislocation display validEtching is effective for dislocation displayPolycrystalline material growthAfter-treatment detailsWater bathsWafering

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Methods and apparatus for the optimization of photo resist etching in a plasma processing system

InactiveUS6949469B1Minimize the differenceSemiconductor/solid-state device manufacturingResistFluorine containing

In a plasma processing system, a method of minimizing the differences in an etch rate of a photo resist material in different regions of a substrate is disclosed. The method includes introducing the substrate having in sequential order thereon, an underlying layer and the photo-resist layer. The method also includes flowing the etchant gas mixture into a plasma reactor of the plasma processing system, the etchant gas mixture comprising a flow of a fluorine containing gas between about 0.1% and about 10% of the etchant gas mixture. The method further includes striking a plasma from the gas mixture; etching the photo-resist layer with the plasma; and, removing the substrate from the plasma reactor.

Owner:LAM RES CORP

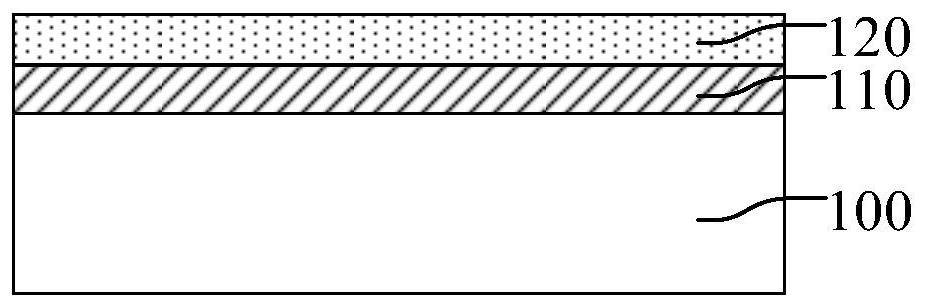

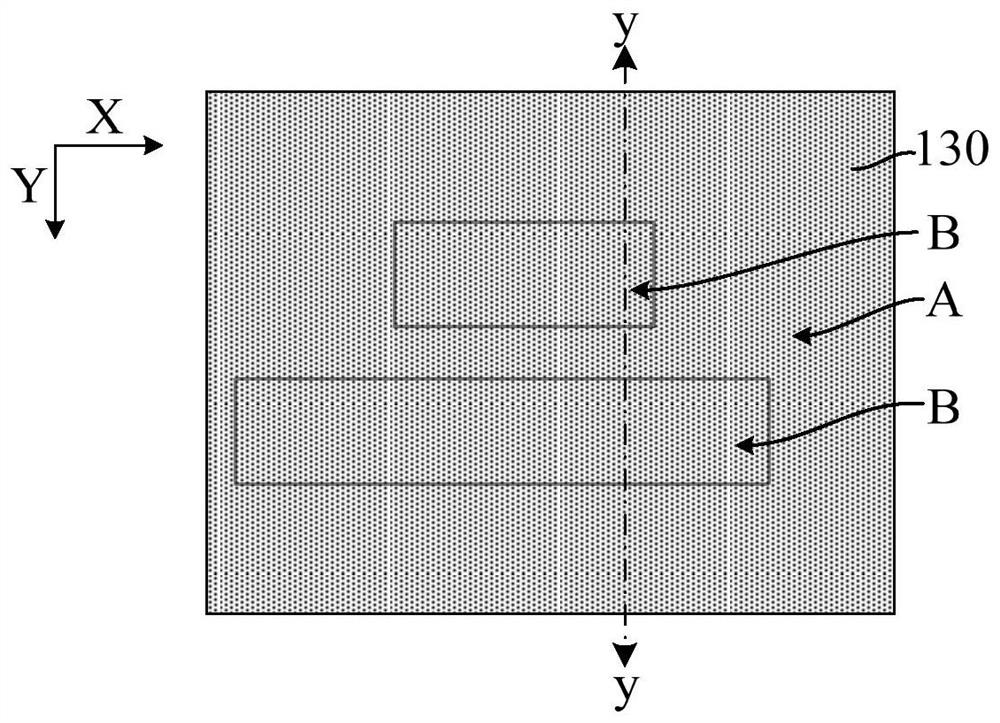

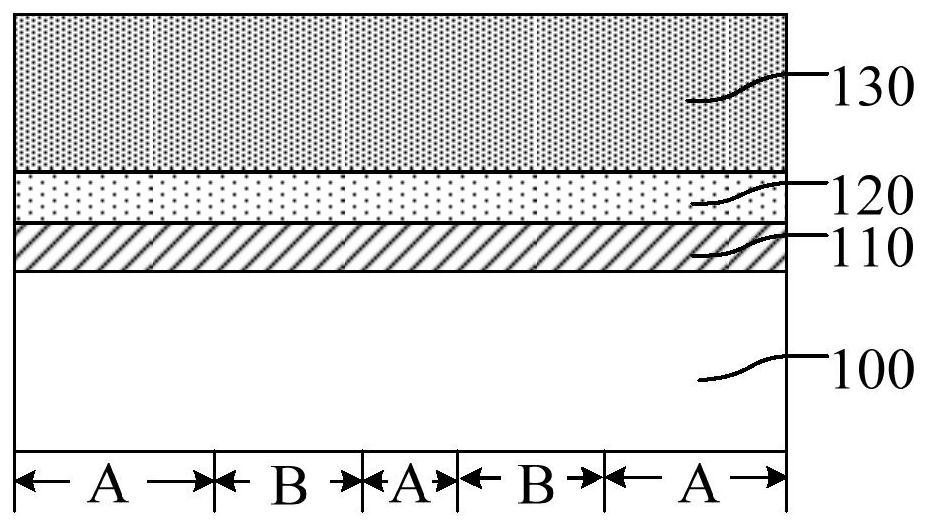

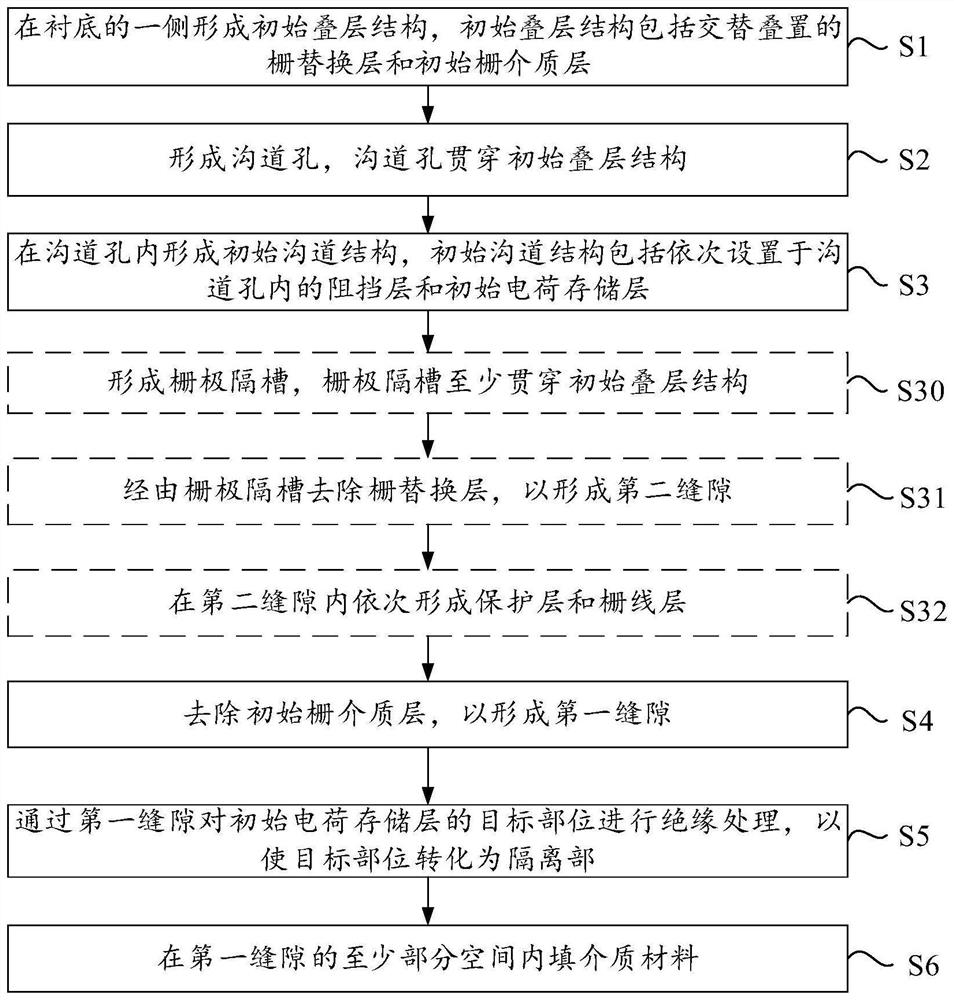

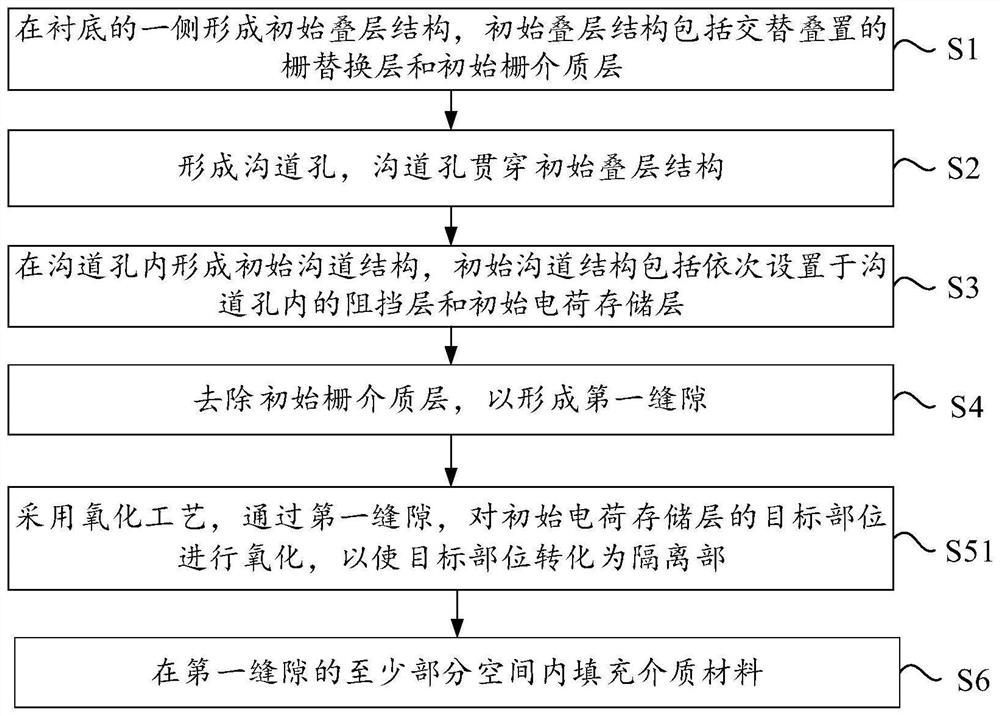

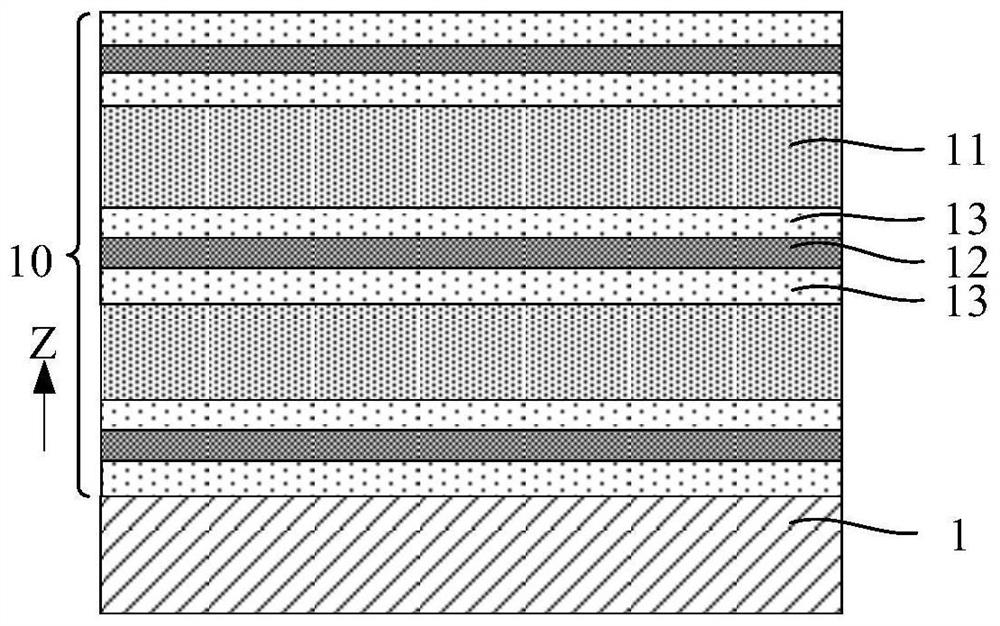

Formation method of semiconductor structure

PendingCN114551333AReduce difficultyImprove process controlSolid-state devicesSemiconductor/solid-state device manufacturingCrystallographySemiconductor structure

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

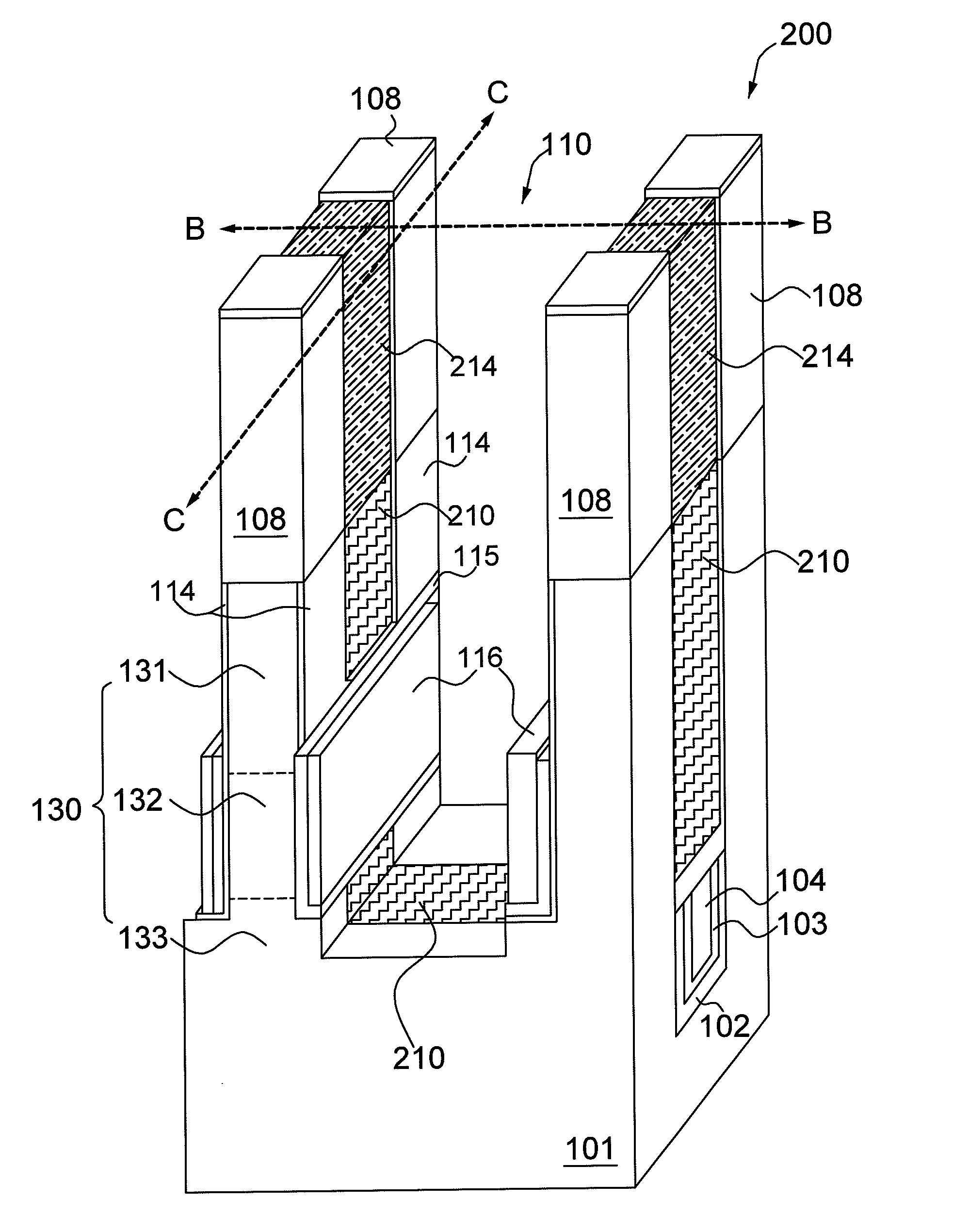

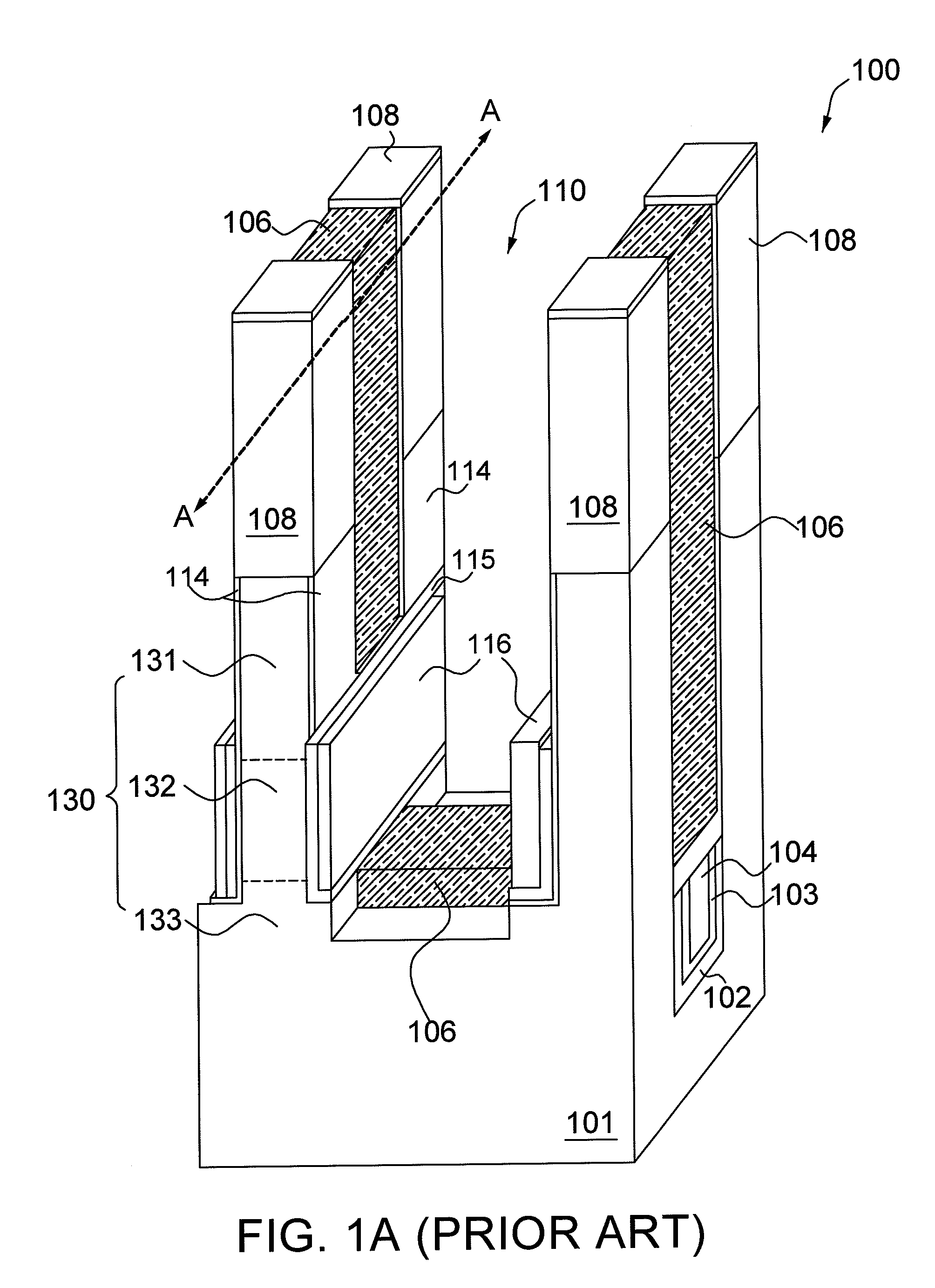

Semiconductor structure and preparation method thereof, three-dimensional memory and storage system

PendingCN114551457AInhibit migrationImprove stabilitySolid-state devicesRead-only memoriesGate dielectricSemiconductor structure

Owner:YANGTZE MEMORY TECH CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap

![Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method](https://images-eureka.patsnap.com/patent_img_release/38585591-87d6-4f06-8e07-ed0eac7d2896/HDA0000721352810000011.PNG)

![Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method](https://images-eureka.patsnap.com/patent_img_release/38585591-87d6-4f06-8e07-ed0eac7d2896/HDA0000721352810000021.PNG)

![Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method Etching solution for dislocation display of monocrystal germanium wafer deflecting to crystal orientation [111] and etching method](https://images-eureka.patsnap.com/patent_img_release/38585591-87d6-4f06-8e07-ed0eac7d2896/HDA0000721352810000022.PNG)