Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7 results about "Dry etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dry etching refers to the removal of material, typically a masked pattern of semiconductor material, by exposing the material to a bombardment of ions (usually a plasma of reactive gases such as fluorocarbons, oxygen, chlorine, boron trichloride; sometimes with addition of nitrogen, argon, helium and other gases) that dislodge portions of the material from the exposed surface. A common type of dry etching is reactive-ion etching. Unlike with many (but not all, see isotropic etching) of the wet chemical etchants used in wet etching, the dry etching process typically etches directionally or anisotropically.

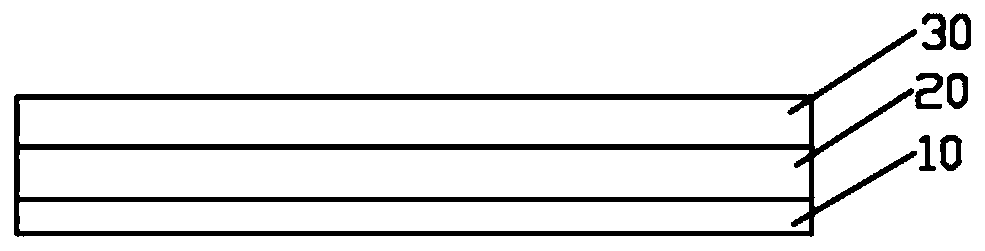

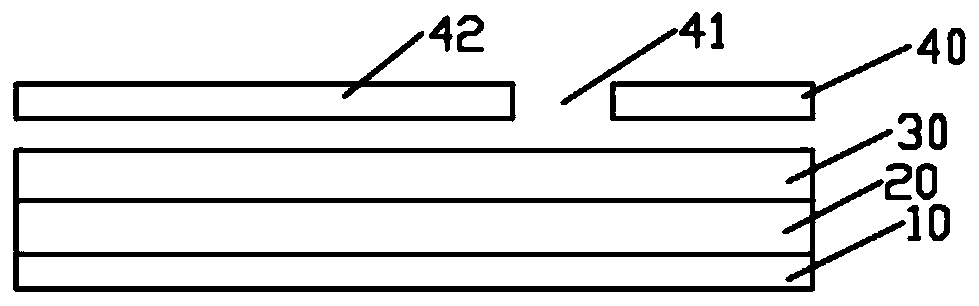

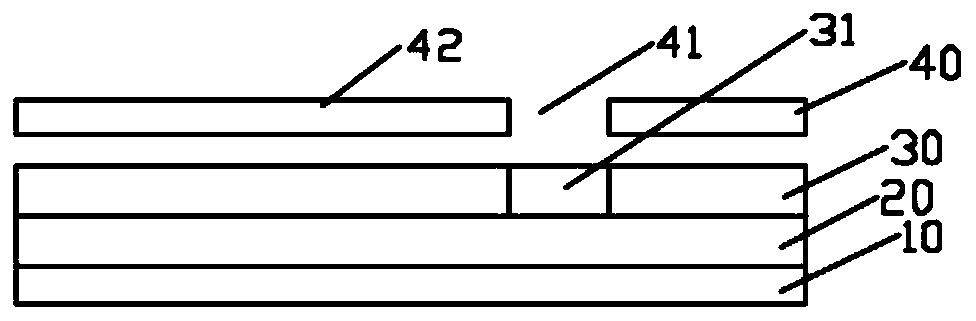

Method of manufacturing semiconductor device capable of sensing dynamic quantity

InactiveUS20020177252A1Avoid stickingEfficient removalSemiconductor/solid-state device manufacturingAcceleration measurementElectricitySilicon on insulator

A method of manufacturing a semiconductor device is provided. The device is manufactured with use of an SOI (Silicon On Insulator) substrate having a first silicon layer, an oxide layer, and a second silicon layer laminated in this order. After forming a trench reaching the oxide layer from the second silicon layer, dry etching is performed, thus allowing the oxide layer located at the trench bottom to be charged at first. This charging forces etching ions to impinge upon part of the second silicon layer located laterally to the trench bottom. Such part is removed, forming a movable section. For example, ions to neutralize the electric charges are administered into the trench, so that the electric charges are removed from charged movable electrodes and their charged surrounding regions. Removing the electric charges prevents the movable section to stick to its surrounding portions.

Owner:DENSO CORP

TFT array substrate manufacture method

ActiveCN105702623AReduce sizeNo short circuit problemSolid-state devicesSemiconductor/solid-state device manufacturingPixel densitySlope angle

The invention provides a TFT (Thin Film Transistor) array substrate manufacture method which comprises the following steps: coating and forming a flat layer on source electrodes and drain electrodes; instead of processing via holes, depositing and patterning a common electrode layer and a passivated protection layer; forming via holes in the passivated protection layer so as to expose the flat layer, and then ashing the flat layer so as to expose the drain electrodes. Compared with a conventional method by which the common electrode layer is deposited and patterned after the via holes are formed in the flat layer, the TFT array substrate manufacture method described in the invention is advantageous in that no electrically conductive material will be left in the via holes of the flat layer when the common electrode layer is patterned, and therefore no short circuit problem will occur in the via holes of the flat layer; the via holes are formed in the flat layer in a pixel region by a means of dry etching through ashing operation, the formed via holes are allowed to have large slope angles, and therefore the size of a TFT can be reduced to a certain extent and and pixel density can be improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Pallet system used for plasma dry etching

InactiveCN105448776AEasy to disperseIncrease etch rateElectric discharge tubesSemiconductor/solid-state device manufacturingMetallurgyCvd graphene

The invention relates to the technical field of semiconductor processing and provides a pallet system used for plasma dry etching, which introduces a grapheme material or grapheme composite material layer to improve the surface heat dissipation capability and the temperature uniformity of a wafer. The pallet system comprises an aluminum pallet, helium hole, a sealing ring, a cover plate and the embedded grapheme material (or grapheme composite material) layer high in heat conductivity. The pallet system has the advantages and active effects that: the high-heat-conductivity grapheme material or grapheme composite material are used in the pallet system used for the r plasma dry etching, the instant heat dissipation capability of the wafer in the etching process is substantially improved, the temperature uniformity of the surface of the wafer is conveniently controlled, the qualified rate of etched products is improved, and the operation window of the etching process is enlarged.

Owner:SINO NITRIDE SEMICON

Polysiloxane, method of manufacturing same, silicon-containing alicyclic compound, and radiation-sensitive resin composition

InactiveUS6846895B2Silicon organic compoundsPhotosensitive materials for photomechanical apparatusResistHalogen

A novel polysiloxane having the following structural units (I) and / or (II) and the structural unit (III), wherein A1 and A2 are an acid-dissociable monovalent organic group, R1 is hydrogen, monovalent (halogenated) hydrocarbon, halogen, or amino, R2 is monovalent (halogenated) hydrocarbon group, or halogen. A method of preparing such a polysiloxane, a silicon-containing alicyclic compound providing this polysiloxane, and a radiation-sensitive resin composition comprising this polysiloxane are also provided. The polysiloxane is useful as a resin component for a resist material, effectively senses radiation with a short wavelength, exhibits high transparency to radiation and superior dry etching properties, and excels in basic resist properties required for resist materials such as high sensitivity, resolution, developability, etc.

Owner:JSR CORPORATIOON

Method for forming gate stack of 3D memory device

ActiveCN110729295AReduce process stepsReduce process complexitySolid-state devicesPhotomechanical apparatusSemiconductor structureIon beam

The invention discloses a method for forming the gate stack of a 3D memory device. The method comprises the following steps that: an insulating stack structure is formed on a semiconductor substrate;a step-shaped mask layer is formed on the insulating laminated structure; a step-shaped insulating laminated structure is formed; and the insulating laminated structure is replaced with a gate laminated structure, and the height of the step-shaped mask layer is set through the material and height of the insulating laminated structure. According to the method of the invention, a gray-scale photoetching method, a nanoimprint lithography method, a gray-scale mask plate photoetching method or an ion beam gas-assisted deposition method is adopted to form a step-shaped mask layer; a semiconductor structure is etched by using dry etching, so that the pattern of the mask layer is transferred into the insulating laminated structure; and therefore, process steps are reduced, and process complexity is reduced.

Owner:SHANGHAI IND U TECH RES INST

Manufacturing method of display panel

ActiveCN110634794AImprove reliabilitySolve the problems that easily cause the performance of TFT devices to decline sharply or even failSolid-state devicesSemiconductor/solid-state device manufacturingUltravioletEngineering

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

Preparation method of anodic oxide film

ActiveCN114717628AAccelerated corrosionImprove withstand voltage performanceAnodisationOXALIC ACID DIHYDRATEPhysical chemistry

The invention relates to a preparation method of an anodic oxide film. The preparation method comprises the steps of degreasing treatment, alkali corrosion treatment, neutralization treatment, anodic oxidation treatment, ultrasonic cleaning treatment and hole sealing treatment which are sequentially carried out. By improving process parameters, adopting mixed acid of 6-40 g / L oxalic acid and 14-16 g / L sulfuric acid for anodic oxidation and recombining all basic operations, the corrosion resistance and voltage resistance, especially HCl corrosion resistance, of a coating film can be obviously improved, the problems of corrosion, cracking and the like of an anodic oxide film on the surface of a part of vacuum dry etching equipment for an OLED are directly solved, and the service life of the vacuum dry etching equipment for the OLED is prolonged. And the service life of the equipment in the cavity is obviously prolonged.

Owner:GUANGDONG KONFOONG MATERIALS INT CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap