Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

15 results about "Ion implantation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

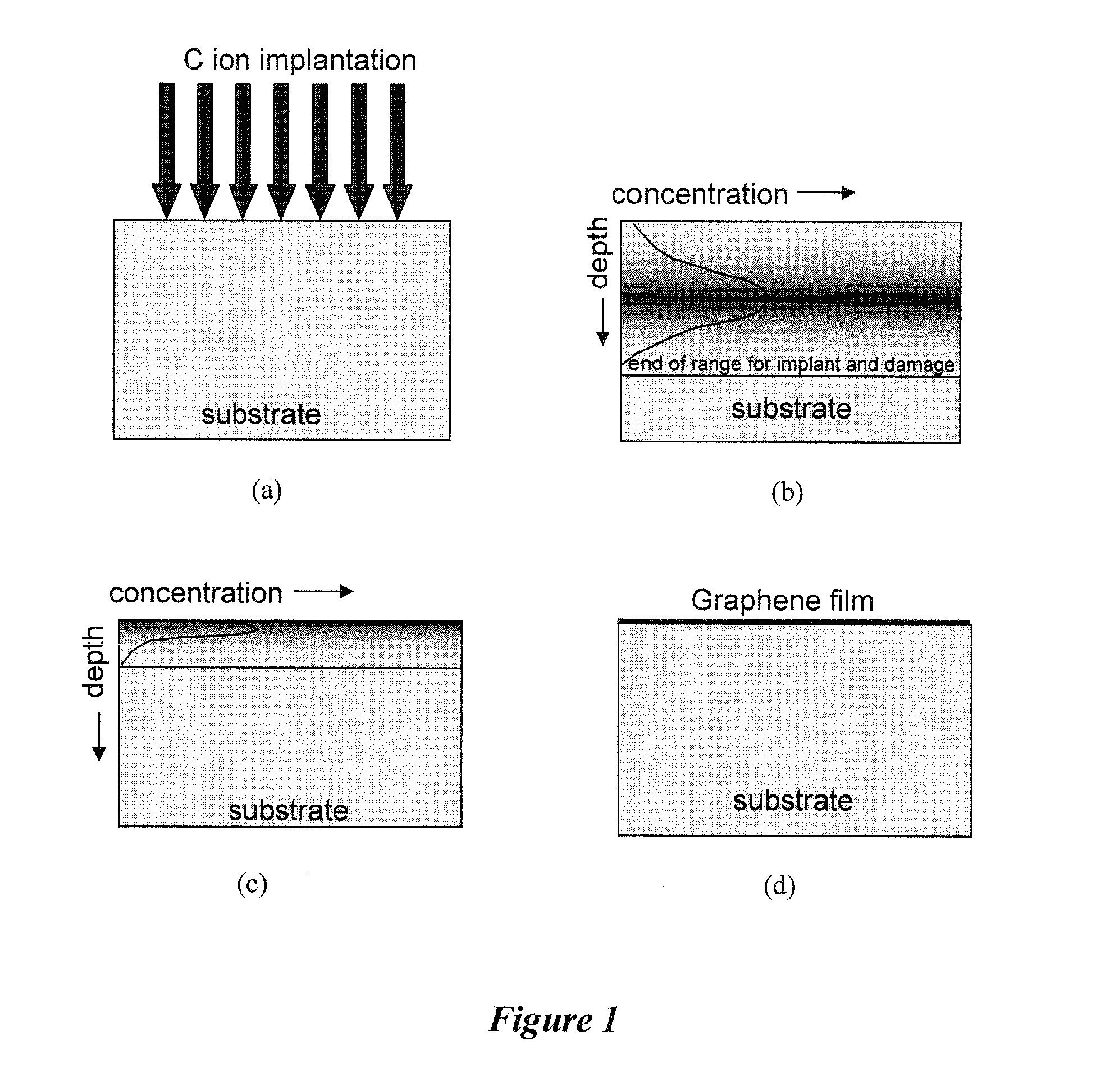

Ion implantation is a low-temperature process by which ions of one element are accelerated into a solid target, thereby changing the physical, chemical, or electrical properties of the target. Ion implantation is used in semiconductor device fabrication and in metal finishing, as well as in materials science research. The ions can alter the elemental composition of the target (if the ions differ in composition from the target) if they stop and remain in the target. Ion implantation also causes chemical and physical changes when the ions impinge on the target at high energy. The crystal structure of the target can be damaged or even destroyed by the energetic collision cascades, and ions of sufficiently high energy (10s of MeV) can cause nuclear transmutation.

Graphene processing for device and sensor applications

Owner:UNIV OF FLORIDA RES FOUNDATION INC

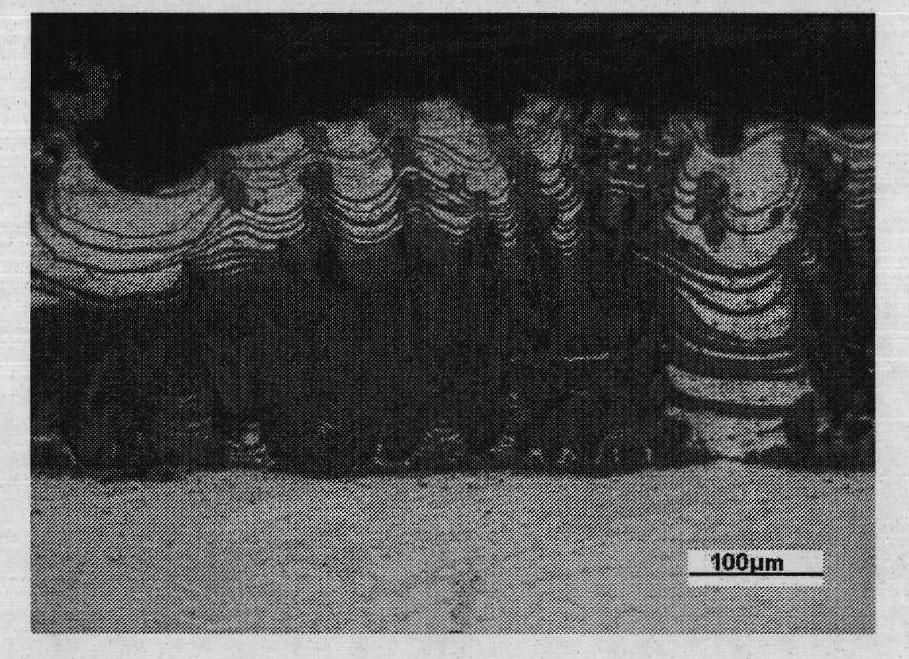

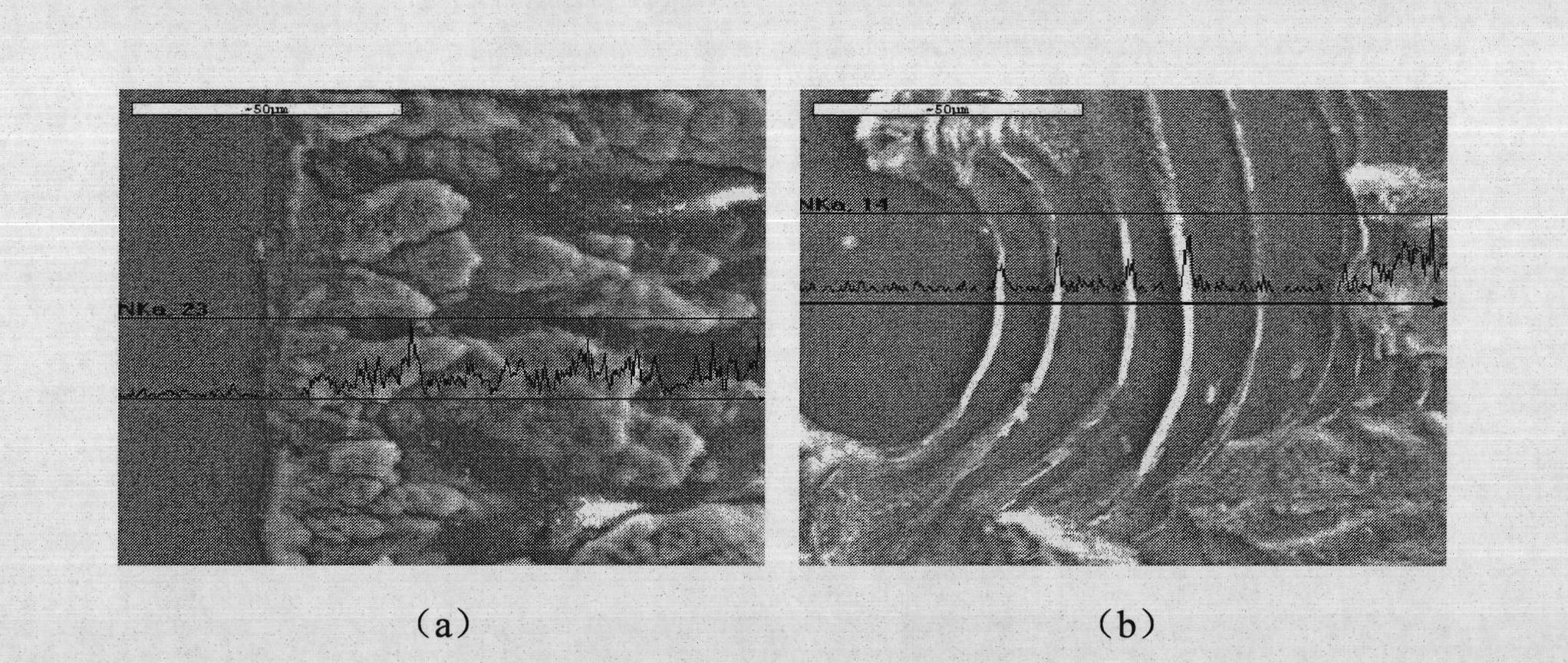

Aluminum and aluminum alloy matrix aluminum nitride reinforced gradient composite surface layer

InactiveCN101880854AImprove wear resistanceSolid state diffusion coatingSurface gradientSurface layer

Owner:JILIN UNIV

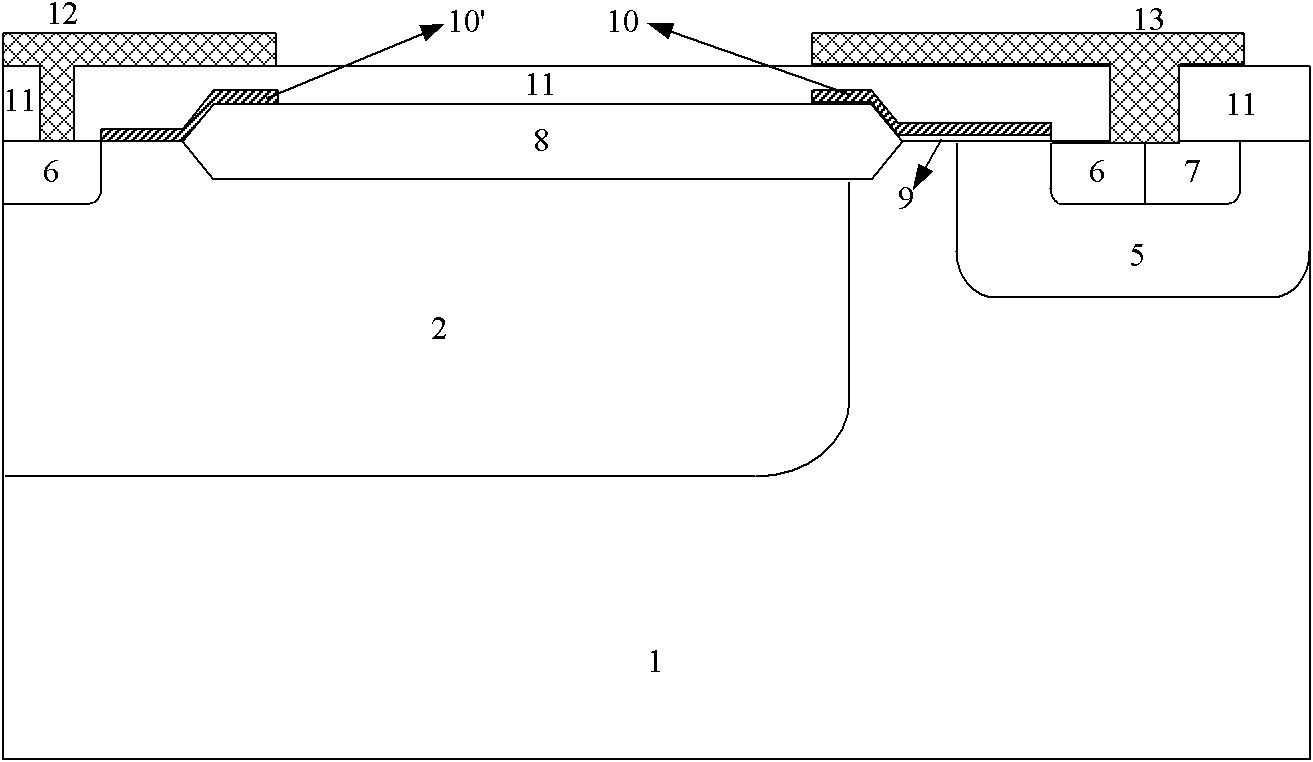

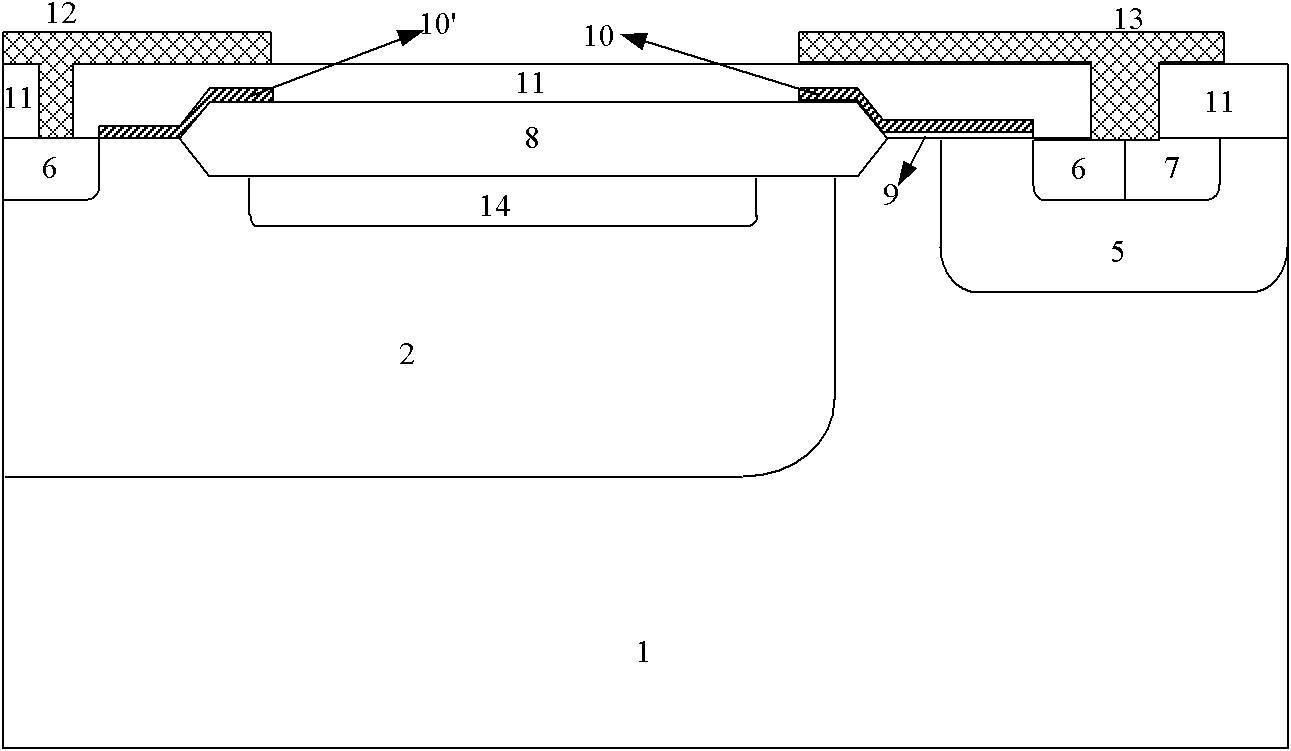

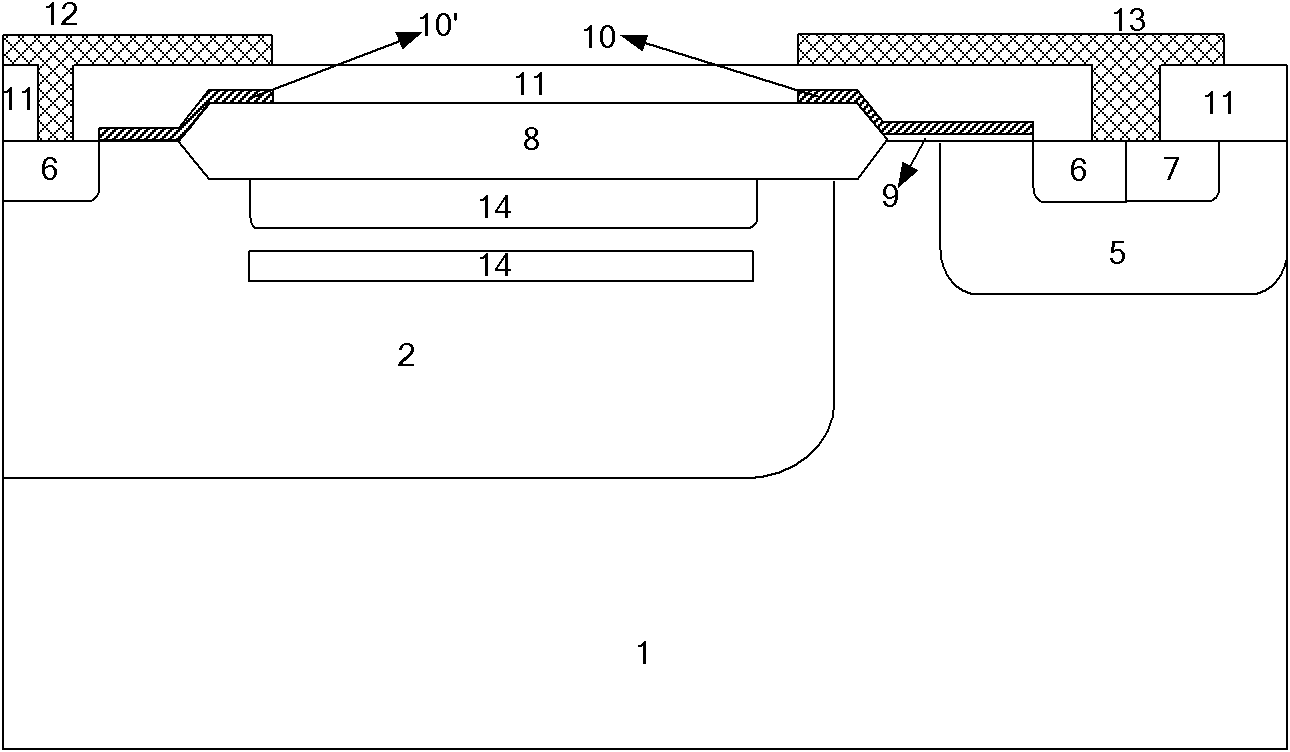

LDMOS (Laterally Diffused Metal Oxide Semiconductor) device with transverse composite buffer layer structure

InactiveCN102184963AImprove performanceImprove pressure resistanceSemiconductor devicesHigh energyIon implantation

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

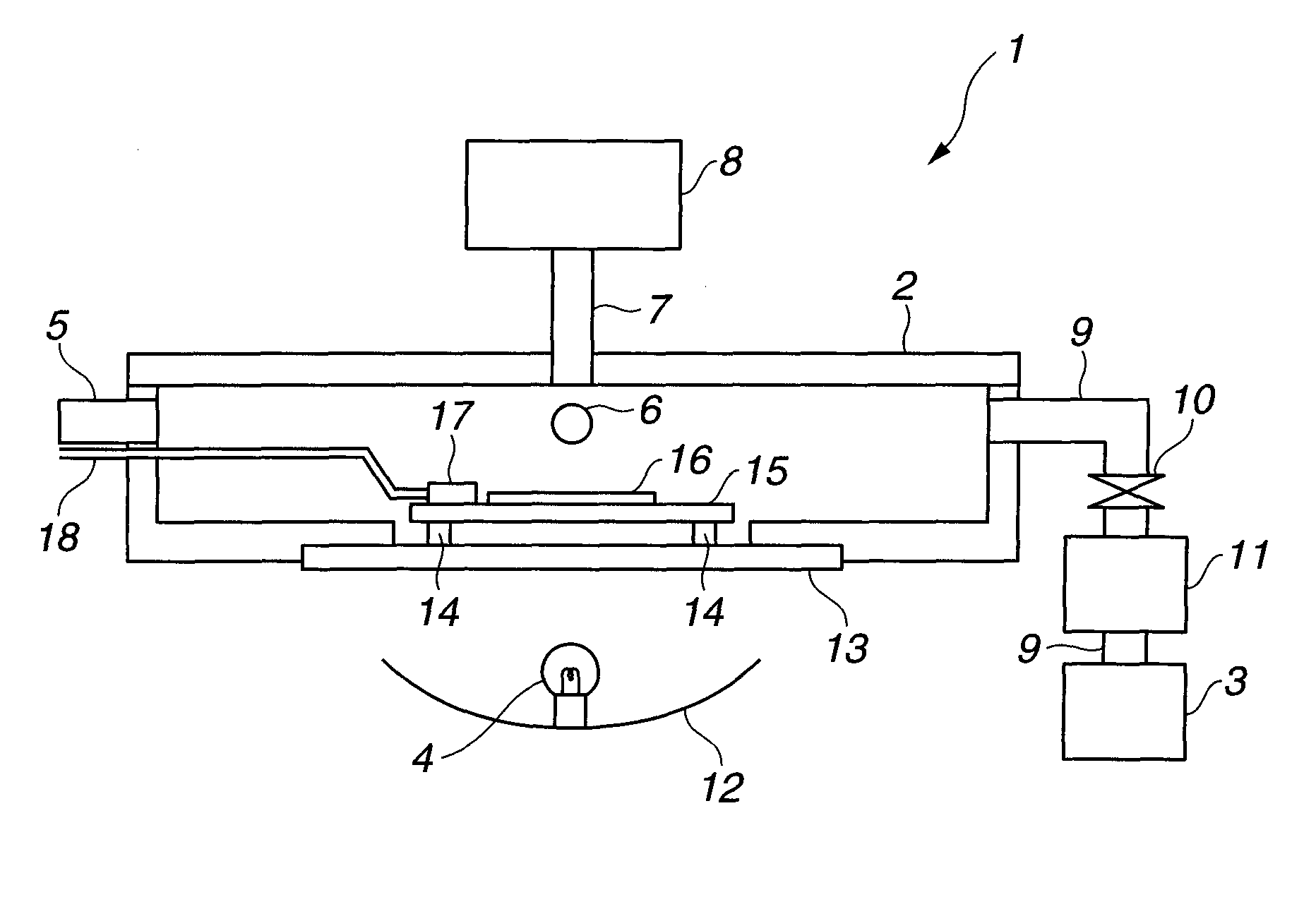

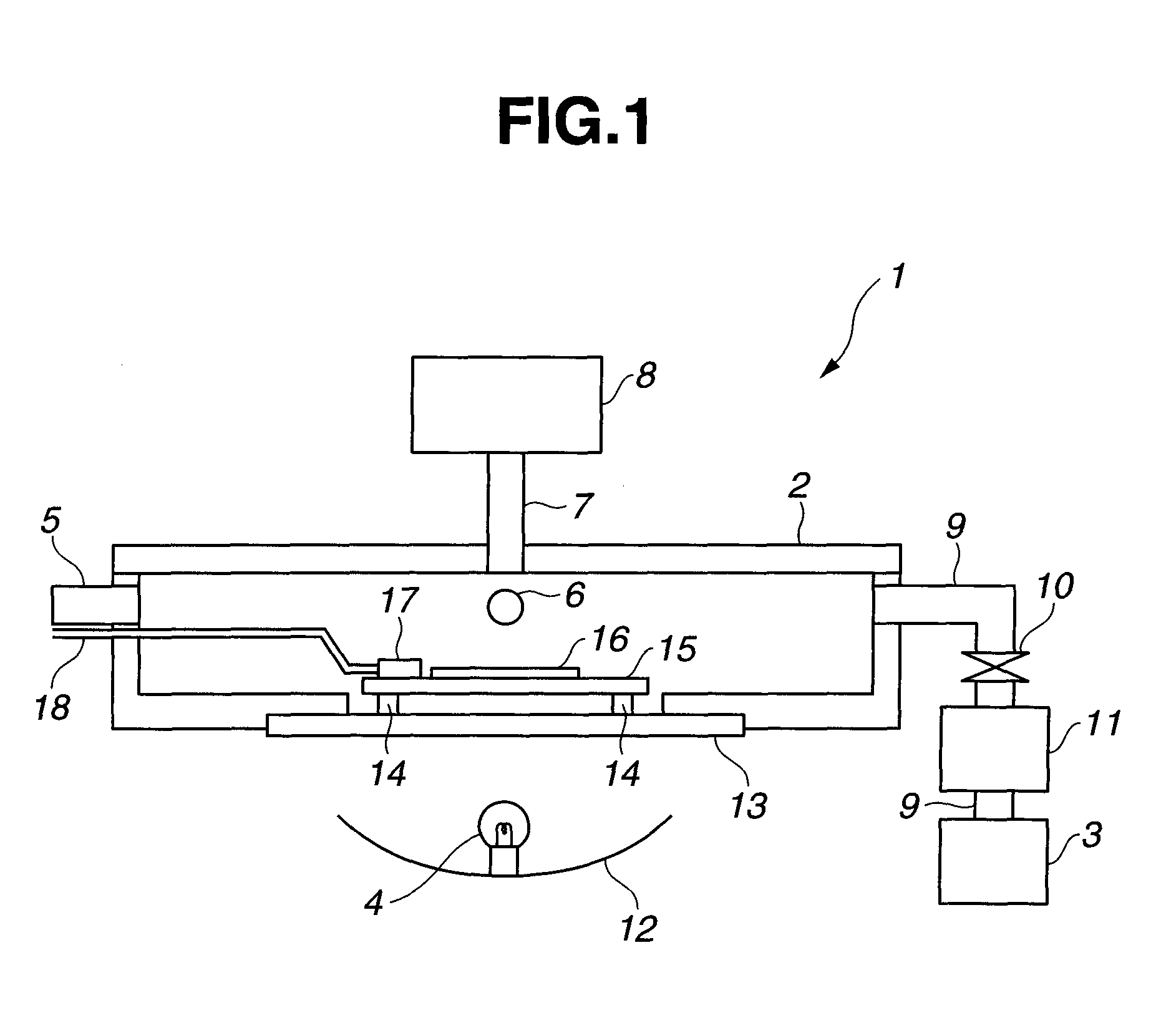

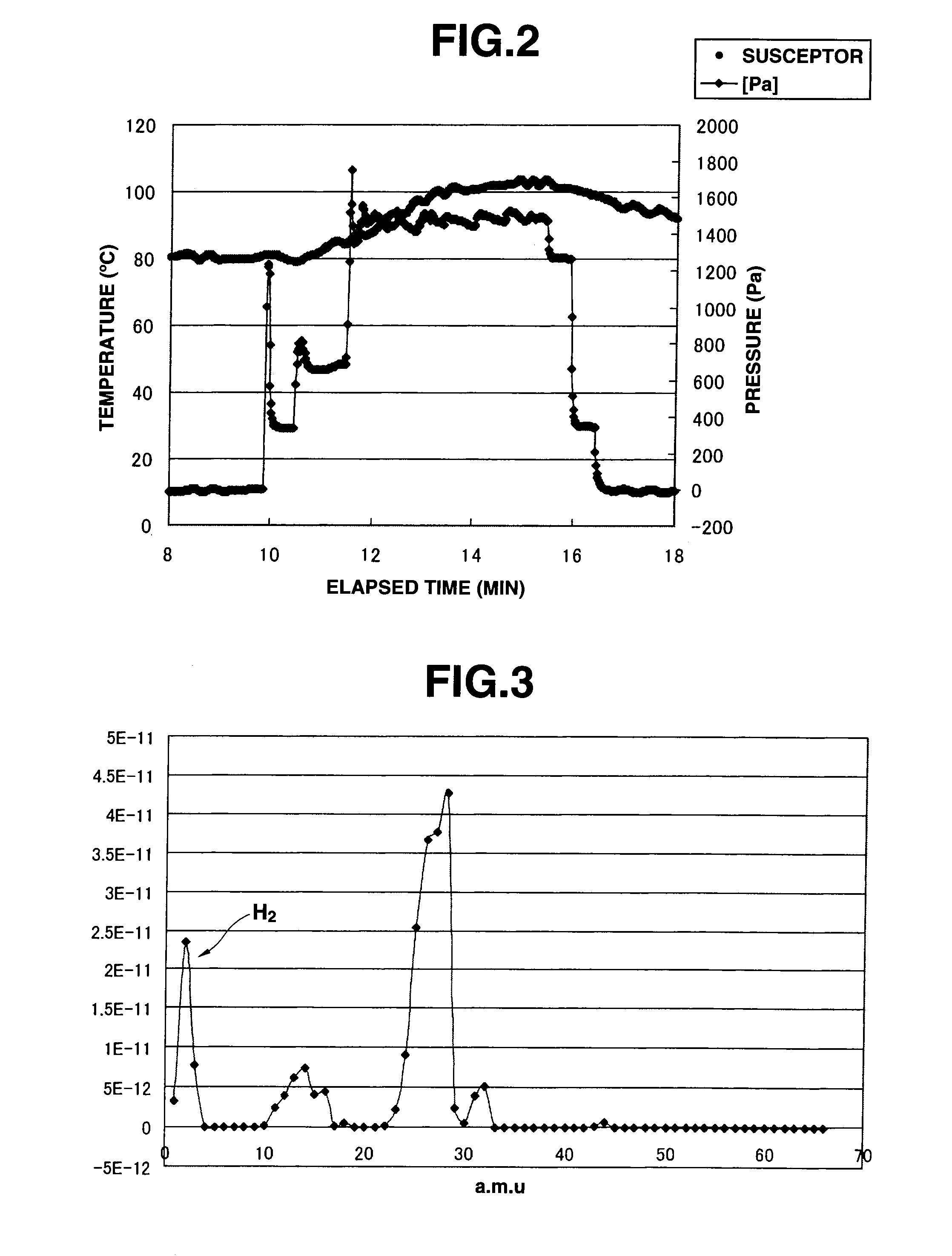

Method of removing resist and apparatus therefor

ActiveUS20100139708A1Easy to moveLow vapor pressureDecorative surface effectsHollow article cleaningResistSusceptor

Owner:MEIDENSHA ELECTRIC MFG CO LTD

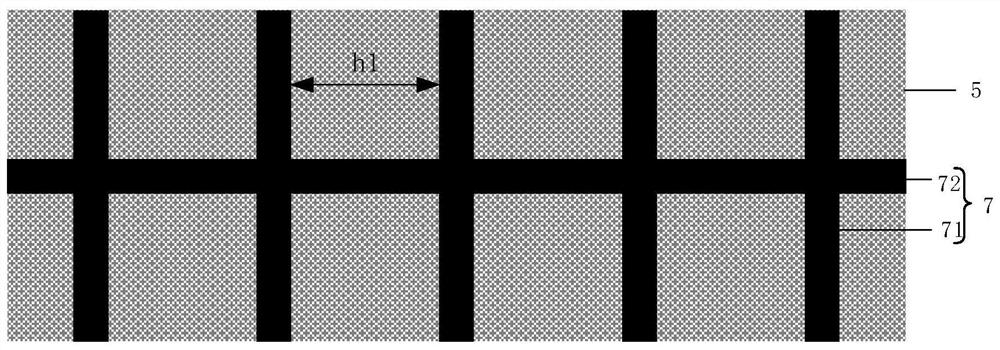

Method of adding auxiliary exposure graph

ActiveCN109407460AReduce defectsImprove stabilityOriginals for photomechanical treatmentGraphicsAlgorithm

The invention discloses a method of adding an auxiliary exposure graph. The method includes acquiring a complete design layout of an original layer; performing OPC (optical proximity correction) on alayout of the current layer according to an acquired original layout graph, and selecting a region of the treated layout graph spacing less than the provision of requirement I; in the selected region,adding an auxiliary exposure graph which has dimensions meeting the provision of requirement II, and no graph is exposed on a silicon wafer; upon adding of the auxiliary exposure graph, if the boundary of photoresist has indentation, allowing the width of the indentation to be less than the provision of requirement III, removing the convex portion of the corresponding original layout graph, and adding the auxiliary exposure graph to a new boundary generated by the removal of the convex portion. The method has the advantages that an ion injection layer process window can be effectively enlarged, graph defects can be decreased, and product yield can be increased.

Owner:SHANGHAI HUALI INTEGRATED CIRCUIT CORP

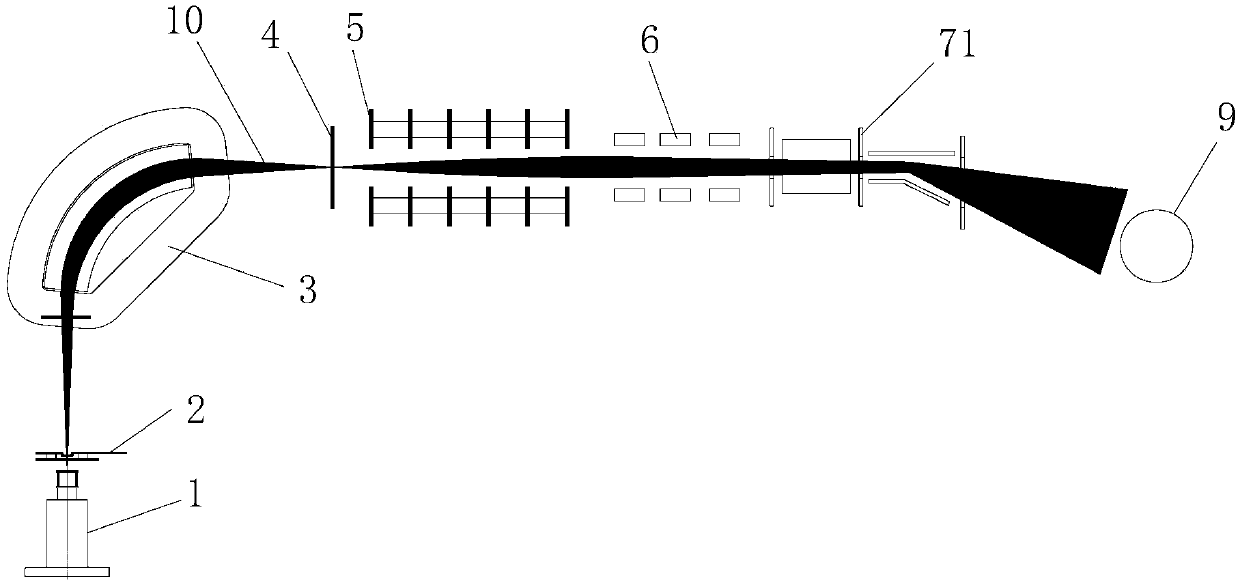

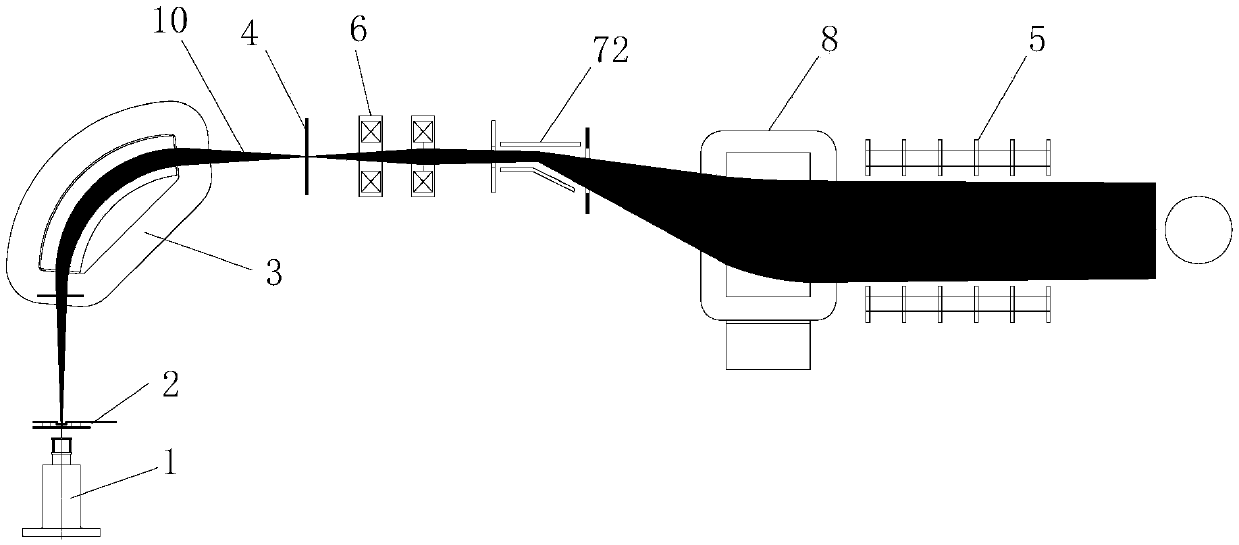

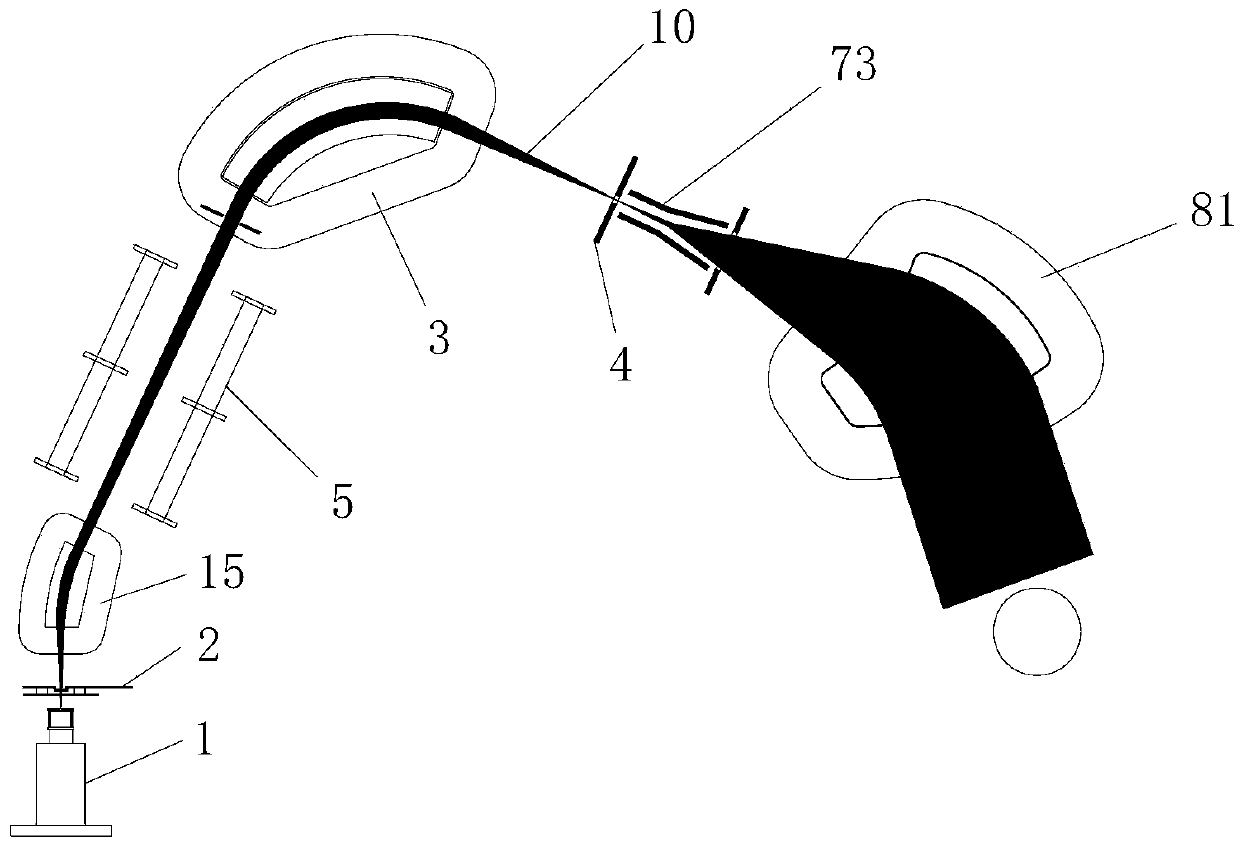

Ion implantation device

ActiveCN111063599AFacilitate multi-level accelerationImprove resolutionElectric discharge tubesSemiconductor/solid-state device manufacturingMedicineWafer

Owner:48TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

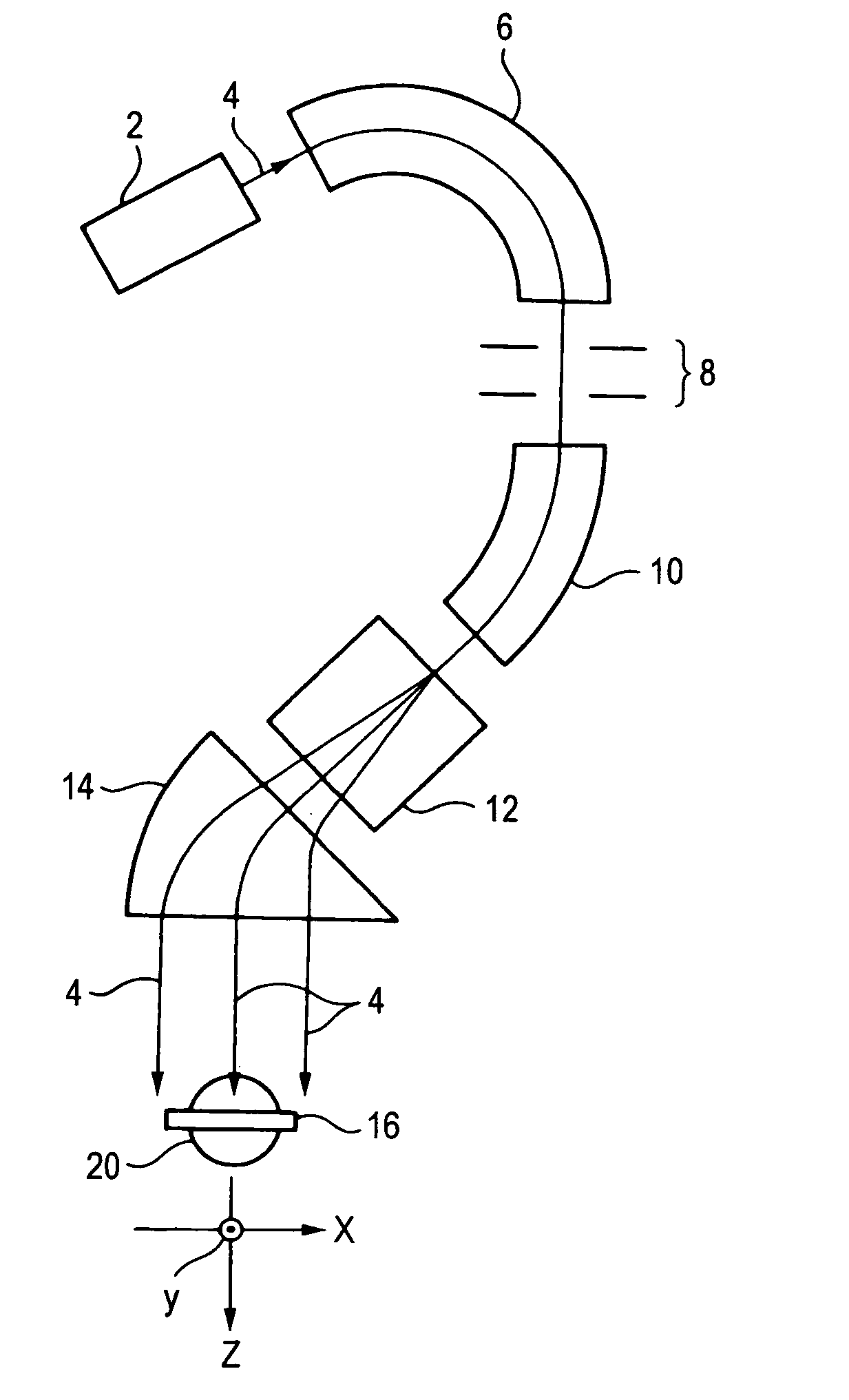

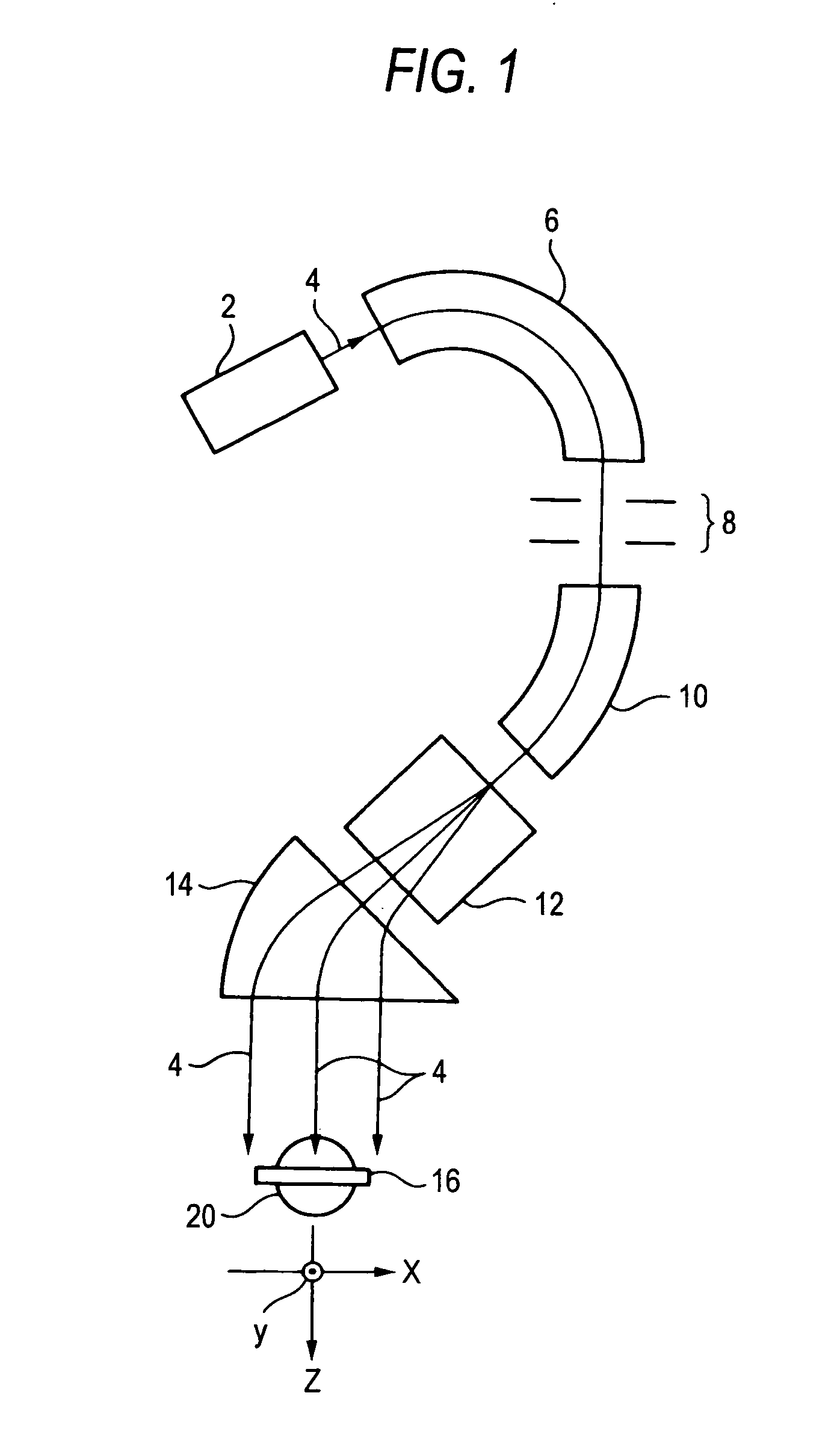

Ion beam measuring method and ion implanting apparatus

Owner:NISSIN ION EQUIP CO LTD

Method for manufacturing semiconductor device

ActiveUS20140357027A1Effectively reducing the SBHReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideGate stack

The present invention discloses a method for manufacturing a semiconductor device, comprising: forming a gate stacked structure on a substrate; forming a source / drain region and a gate sidewall spacer at both sides of the gate stacked structure; depositing a Nickel-based metal layer at least in the source / drain region; performing a first annealing so that the silicon in the source / drain region reacts with the Nickel-based metal layer to form a Ni-rich phase of metal silicide; performing an ion implantation by implanting doping ions into the Ni-rich phase of metal silicide; performing a second annealing so that the Ni-rich phase metal silicide is transformed into a Nickel-based metal silicide, and meanwhile, forming a segregation region of the doping ions at an interface between the Nickel-based metal silicide and the source / drain region. The method according to the present invention performs the annealing after implanting the doping ions into the Ni-rich phase of metal silicide, thereby improving the solid solubility of the doping ions and forming a segregation region of highly concentrated doping ions, thus the SBH of the metal-semiconductor contact between the Nickel-based metal silica and the source / drain region is effectively reduced, the contact resistance is decreased, and the driving capability of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

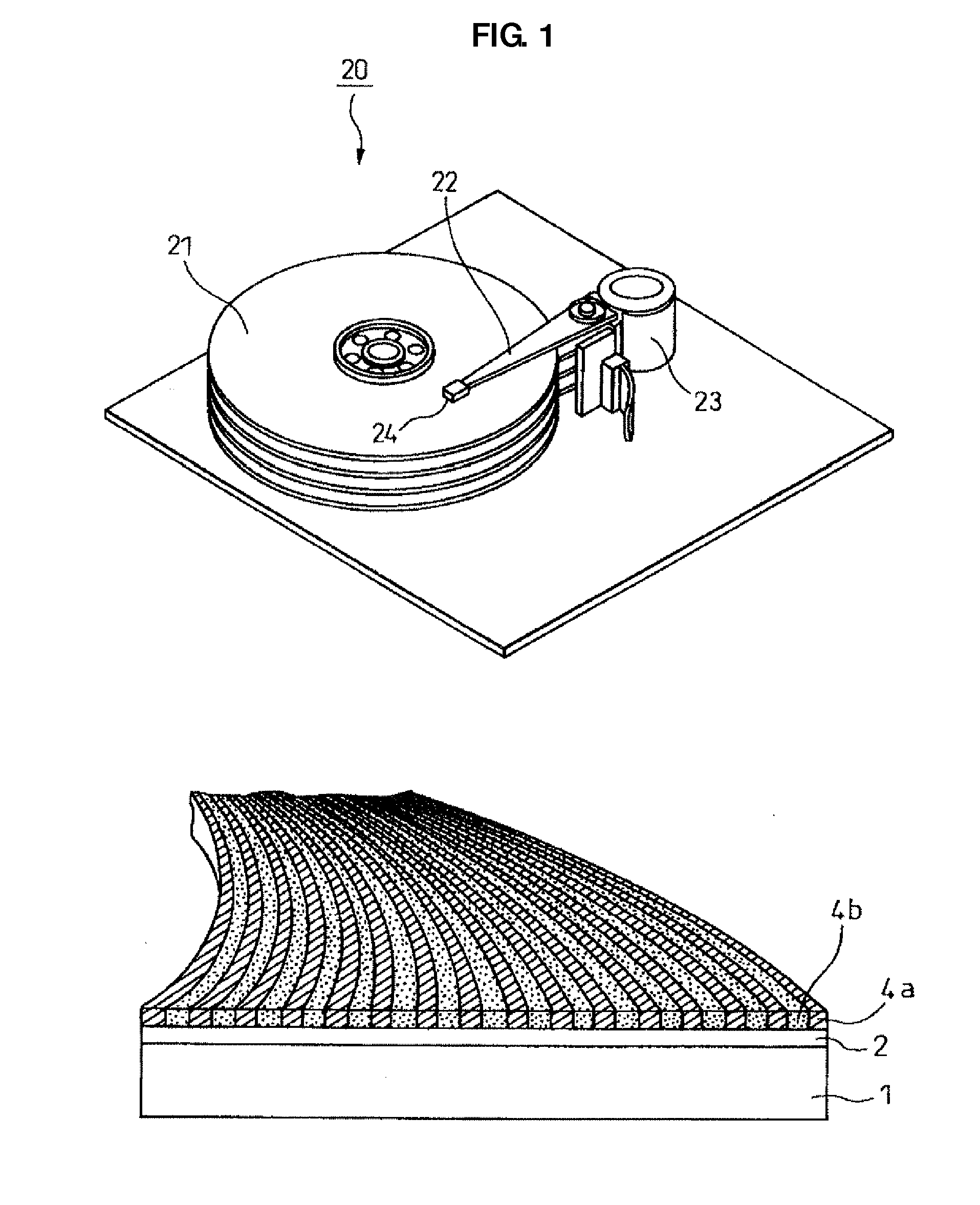

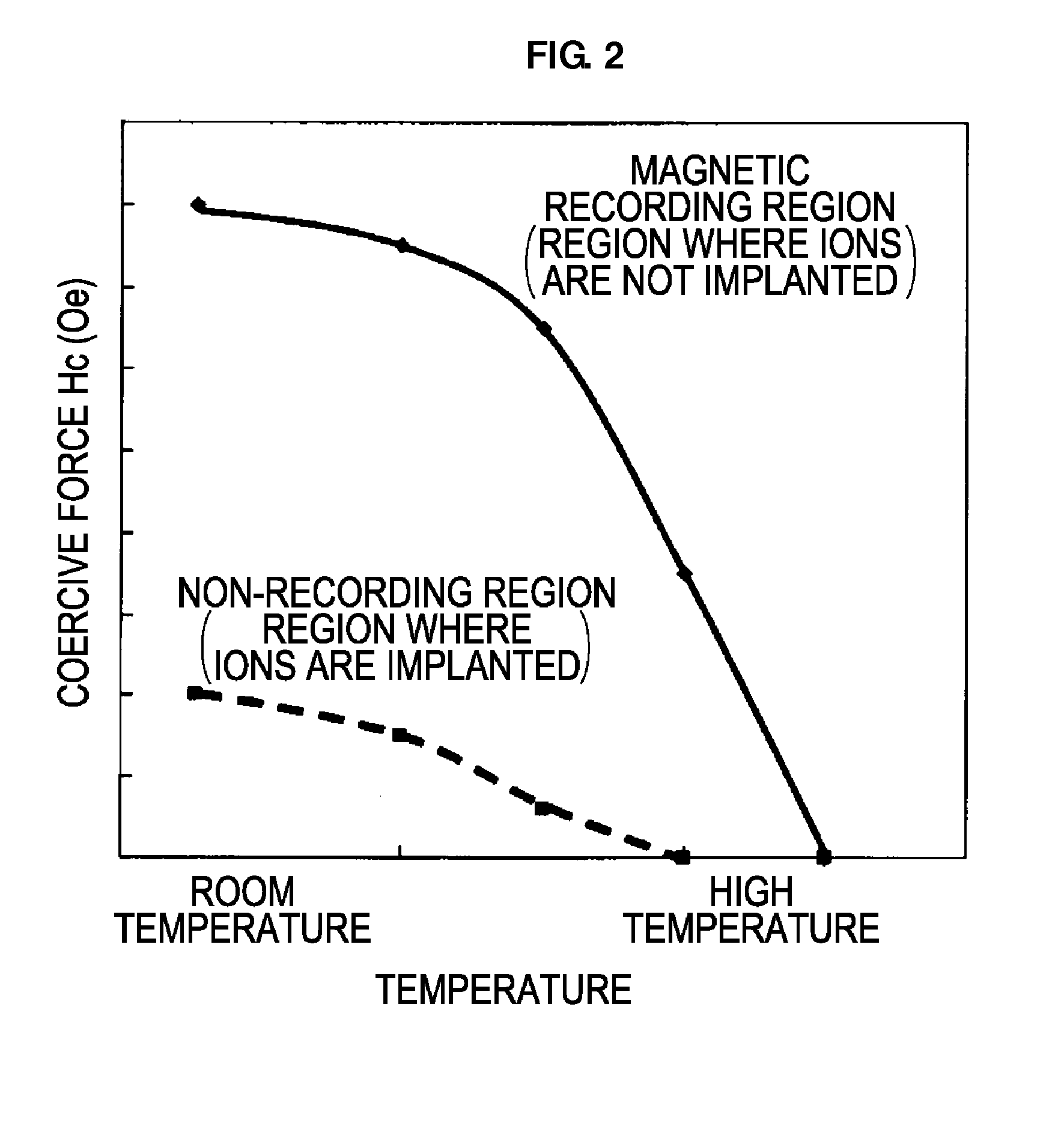

Thermally Assisted Magnetic Recording Disk, Manufacturing Method Thereof, And Magnetic Recording Method

ActiveUS20120075740A1Low coercivitySmall coercive forceNanoinformaticsPatterned record carriersHeat-assisted magnetic recordingCurie temperature

Owner:WESTERN DIGITAL TECH INC

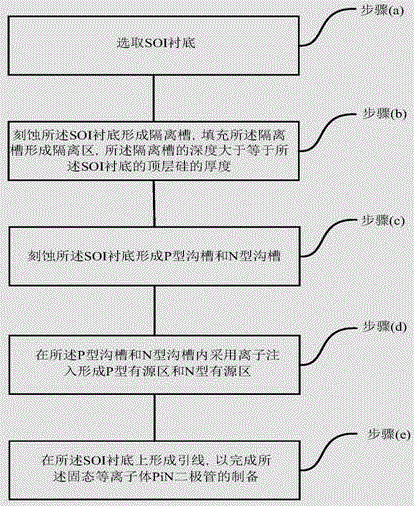

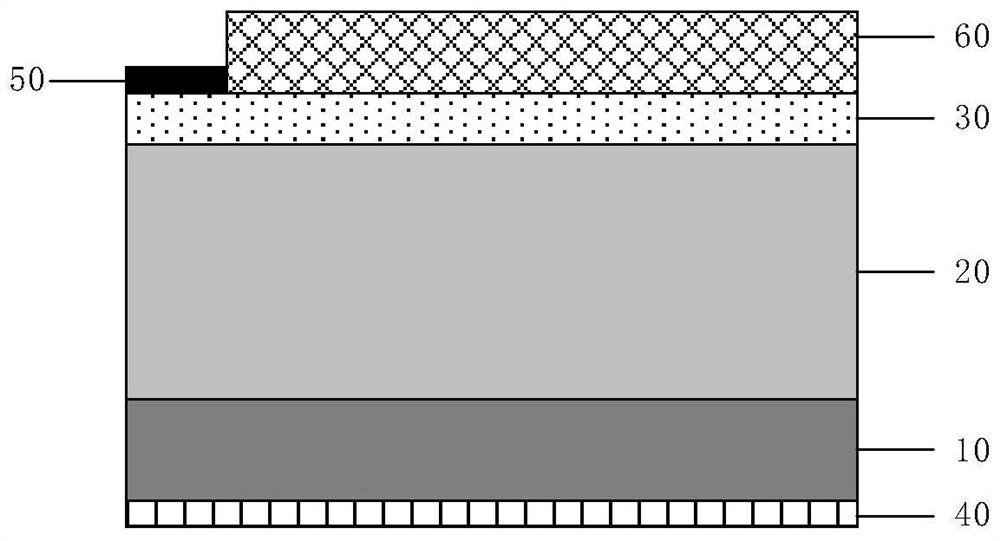

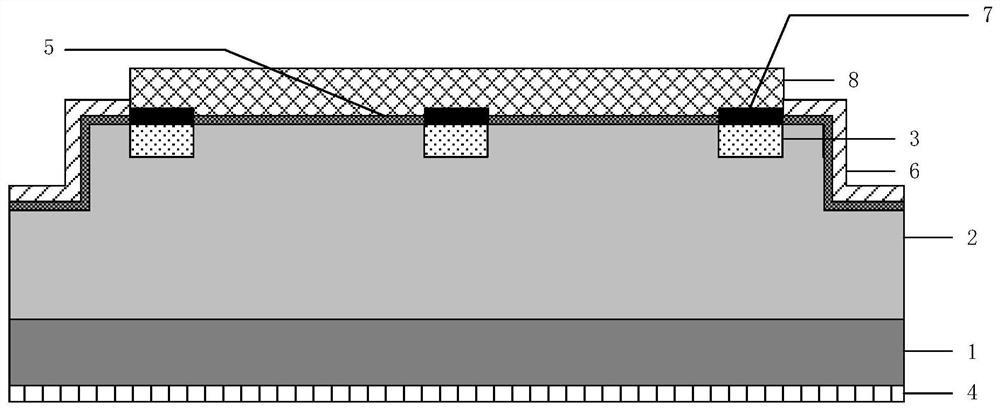

Solid-state plasma PiN diode and preparation method therefor

ActiveCN106783600AImprove breakdown voltagePerformance impactSemiconductor/solid-state device manufacturingSemiconductor devicesPlasma antennaEngineering

Owner:XIDIAN UNIV

Ion injection sample platform

InactiveCN103928282AEasy to controlAvoid radiation damageElectric discharge tubesComputer control systemElectric machine

The invention discloses an ion injection sample platform comprising a seal plate, a sample platform base, stepping motors, sampling plate supports, a gear connecting shaft, a sample plate, a beam current insertion hole, a restraint electrode, insulation posts, a voltage insertion hole and a computer control system. A sample platform body part is formed by sequentially connecting the sample platform base, the stepping motor, the sample plate supports, the stepping motor, the gear connecting shaft and the sample plate from bottom to top. The first stepping motor can push the sample plate supports to move left and right, the second stepping motor can push the gear connecting shaft to rotate and driven the sample plate to rotate, and the first stepping motor and the second stepping motor are connected with the computer control system. The sample plate is connected with the beam current insertion hole. The restraint electrode is fixedly connected with the sample platform base through the insulation posts and connected with the voltage insertion hole through a wire. The sample platform can be controlled through a computer in a long-distance mode, the ion injection sample platform has a horizontal moving function and a rotating function, in the process of ion injection, samples can be rapidly and precisely replaced, and the inclination angle of the samples can be controlled precisely.

Owner:WUHAN UNIV

Ion filling and depositing combined treatment method of rolling bearing ring raceways

ActiveCN104018115AIncreased working surface hardnessImprove wear resistanceSolid state diffusion coatingEngineeringHardness

Owner:HUANGSHAN MINGMINGDE BEARING

Method for fabricating MOS field effect transistor

InactiveUS20050142720A1Semiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorImpurity

A method of fabricating a MOS field effect transistor. A gate insulating film and a gate conductive film are formed on a semiconductor substrate. The gate conductive film is patterned to form a first gate conductive film having a thin thickness and a second gate conductive film having a thick thickness. An insulating film pattern is formed on a side wall of the second gate conductive film. The insulating film pattern is used as an etching mask to remove exposed portions of the first gate conductive film and the gate insulating film. An etch process is performed to remove the insulating film pattern and a portion of the gate insulating film under the first gate conductive film. An ion implantation process is performed using the first gate conductive film as an ion implantation buffer for a lightly doped impurity region to form a source / drain region.

Owner:DONGBU ELECTRONICS CO LTD

Planar PiN-type beta irradiation battery with passivation layer surface field and preparation method of planar PiN-type beta irradiation battery

PendingCN113990550AImprove energy conversion efficiencyImprove conversion efficiencyRadiation electrical energyOhmic contactFill factor

Owner:XIDIAN UNIV

A thyristor

InactiveCN109273361AExtended service lifeEasy to prepareThyristorSemiconductor/solid-state device manufacturingThyratronSemiconductor

Owner:NANTONG MINICHIP MICRO ELECTRONICS

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap