Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

21 results about "Semiconductor structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fabrication of graphene nanoelectronic devices on SOI structures

ActiveUS20110114918A1Eliminates thermal budget limitationGood substrateSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureGraphene

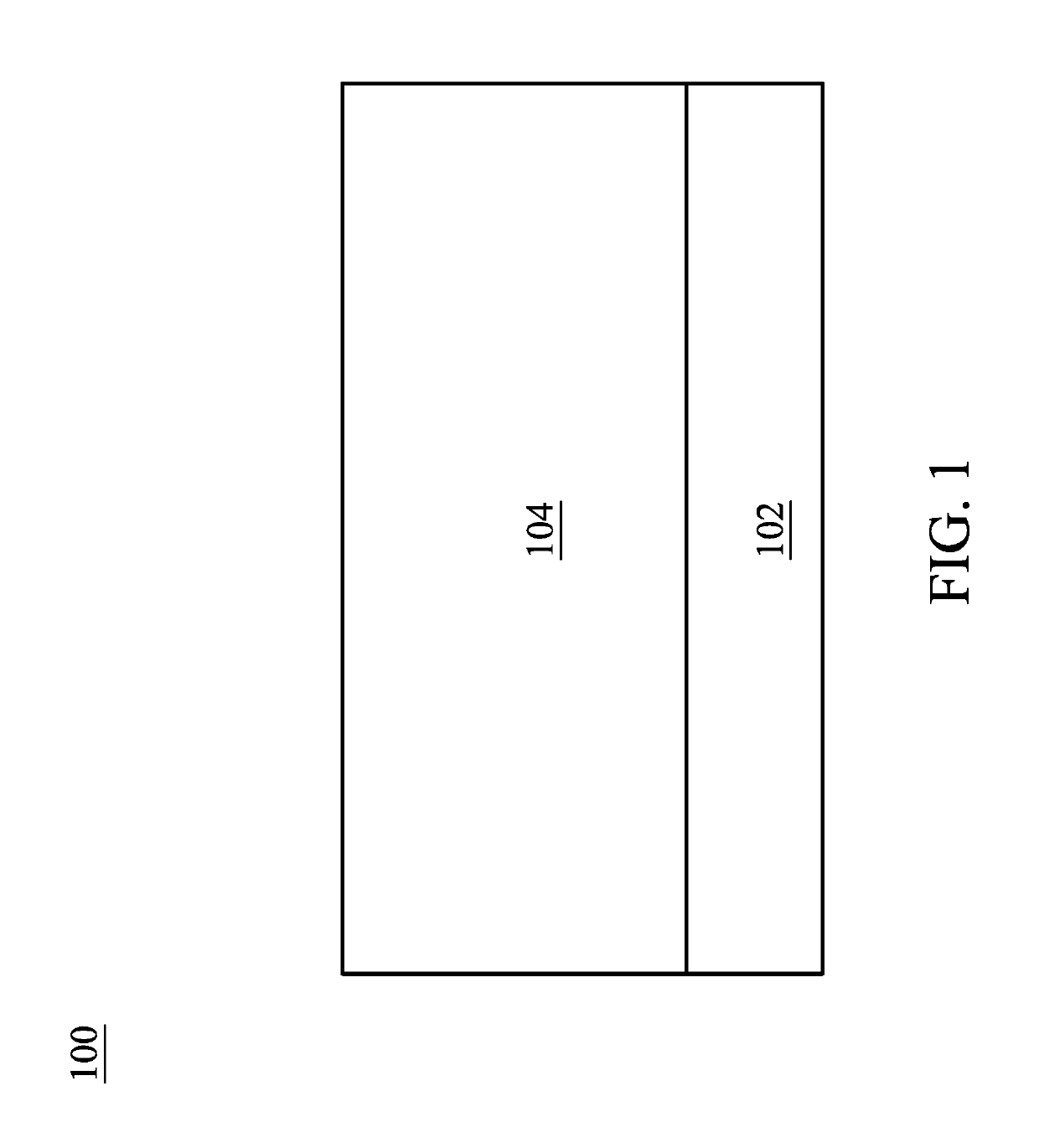

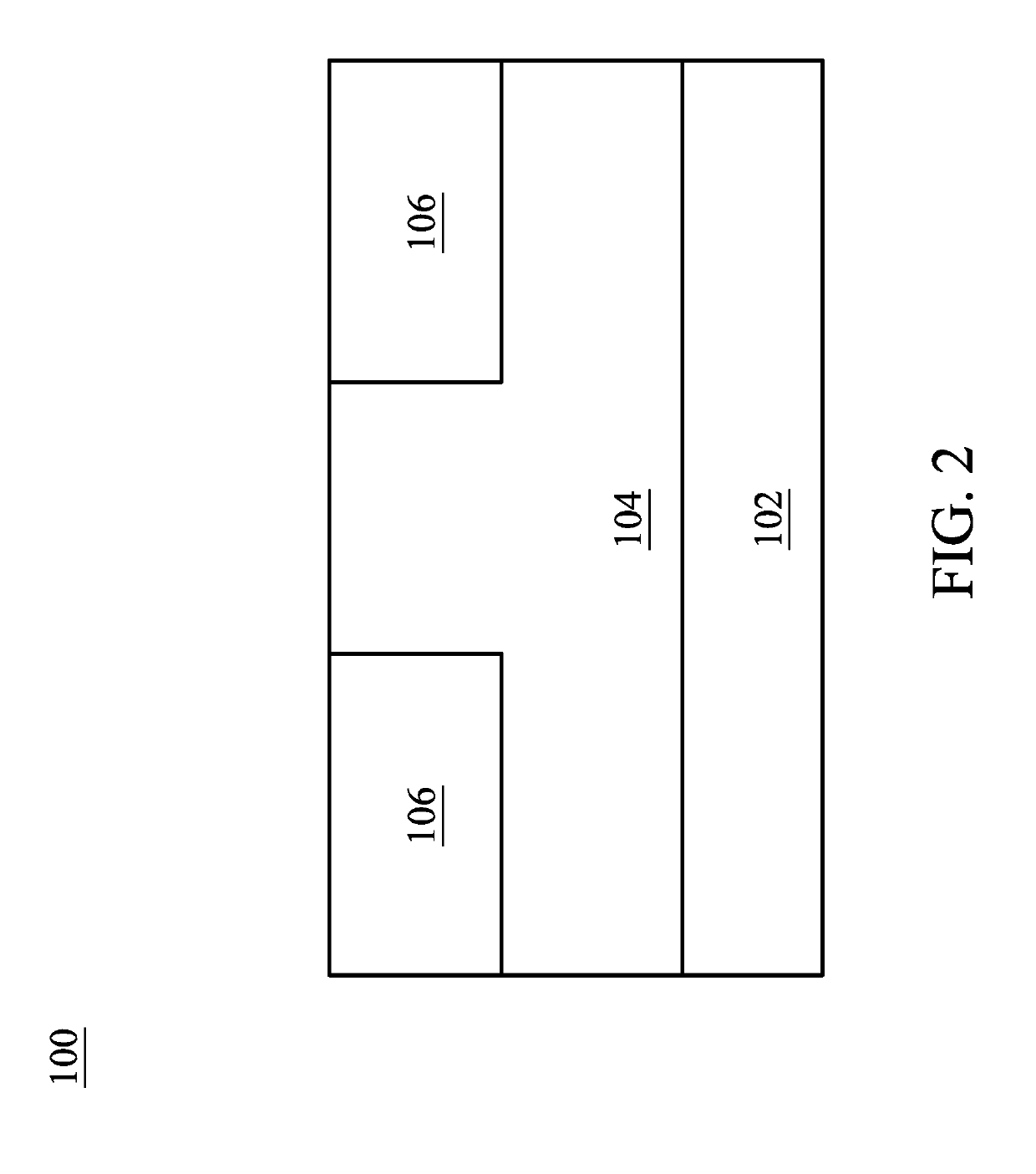

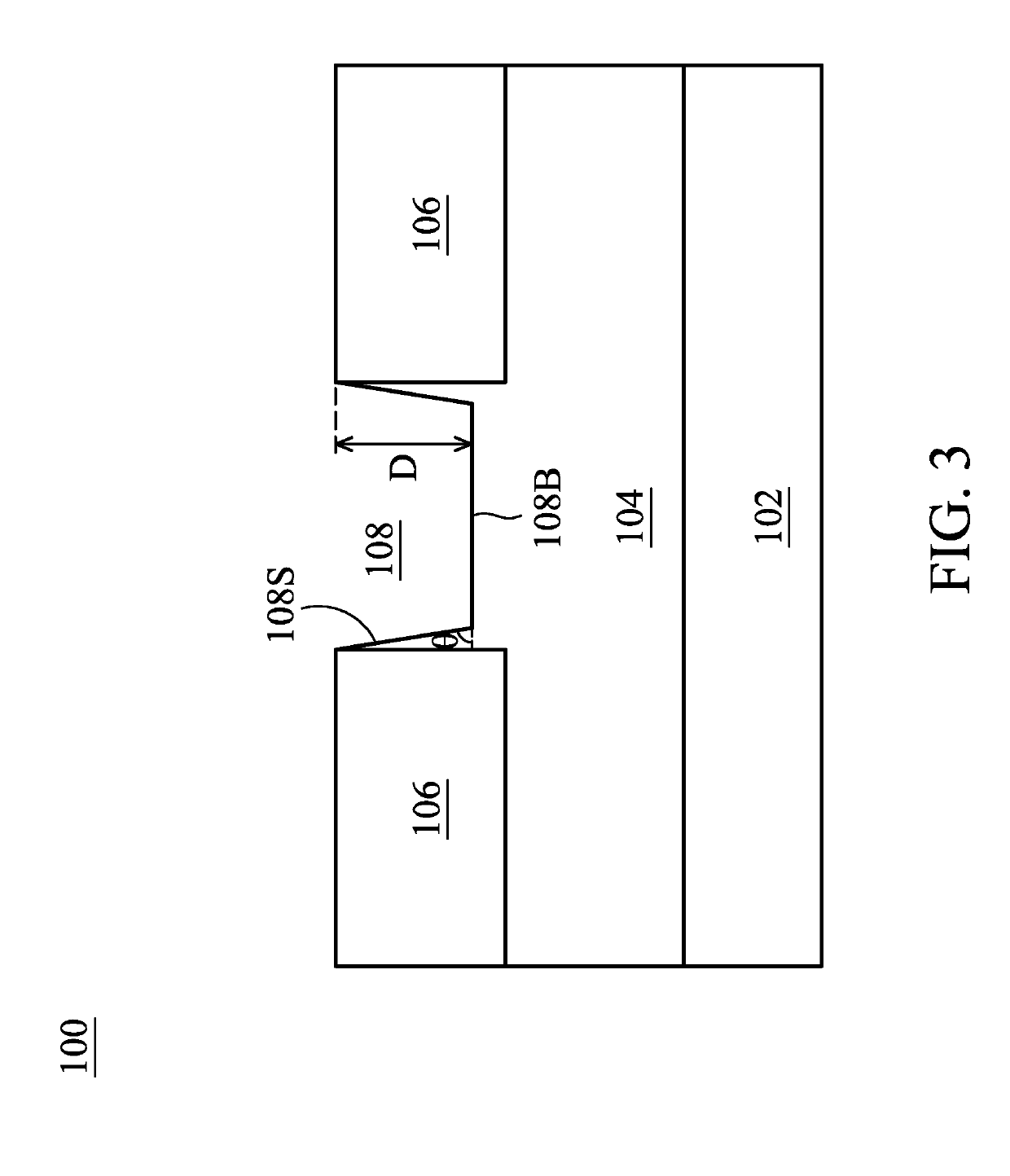

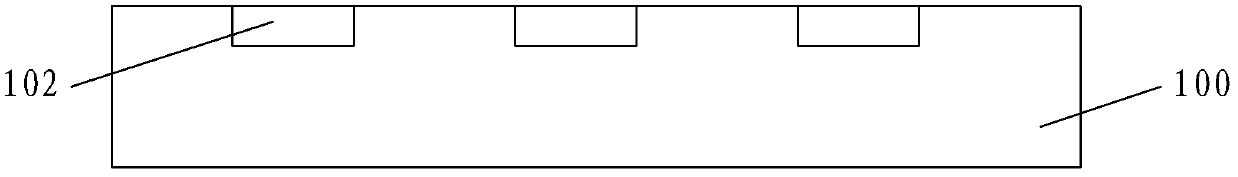

A semiconductor-on-insulator structure and a method of forming the silicon-on-insulator structure including an integrated graphene layer are disclosed. In an embodiment, the method comprises processing a silicon material to form a buried oxide layer within the silicon material, a silicon substrate below the buried oxide, and a silicon-on-insulator layer on the buried oxide. A graphene layer is transferred onto the silicon-on-insulator layer. Source and drain regions are formed in the silicon-on-insulator layer, and a gate is formed above the graphene. In one embodiment, the processing includes growing a respective oxide layer on each of first and second silicon sections, and joining these silicon sections together via the oxide layers to form the silicon material. The processing, in an embodiment, further includes removing a portion of the first silicon section, leaving a residual silicon layer on the bonded oxide, and the graphene layer is positioned on this residual silicon layer.

Owner:GLOBALFOUNDRIES U S INC

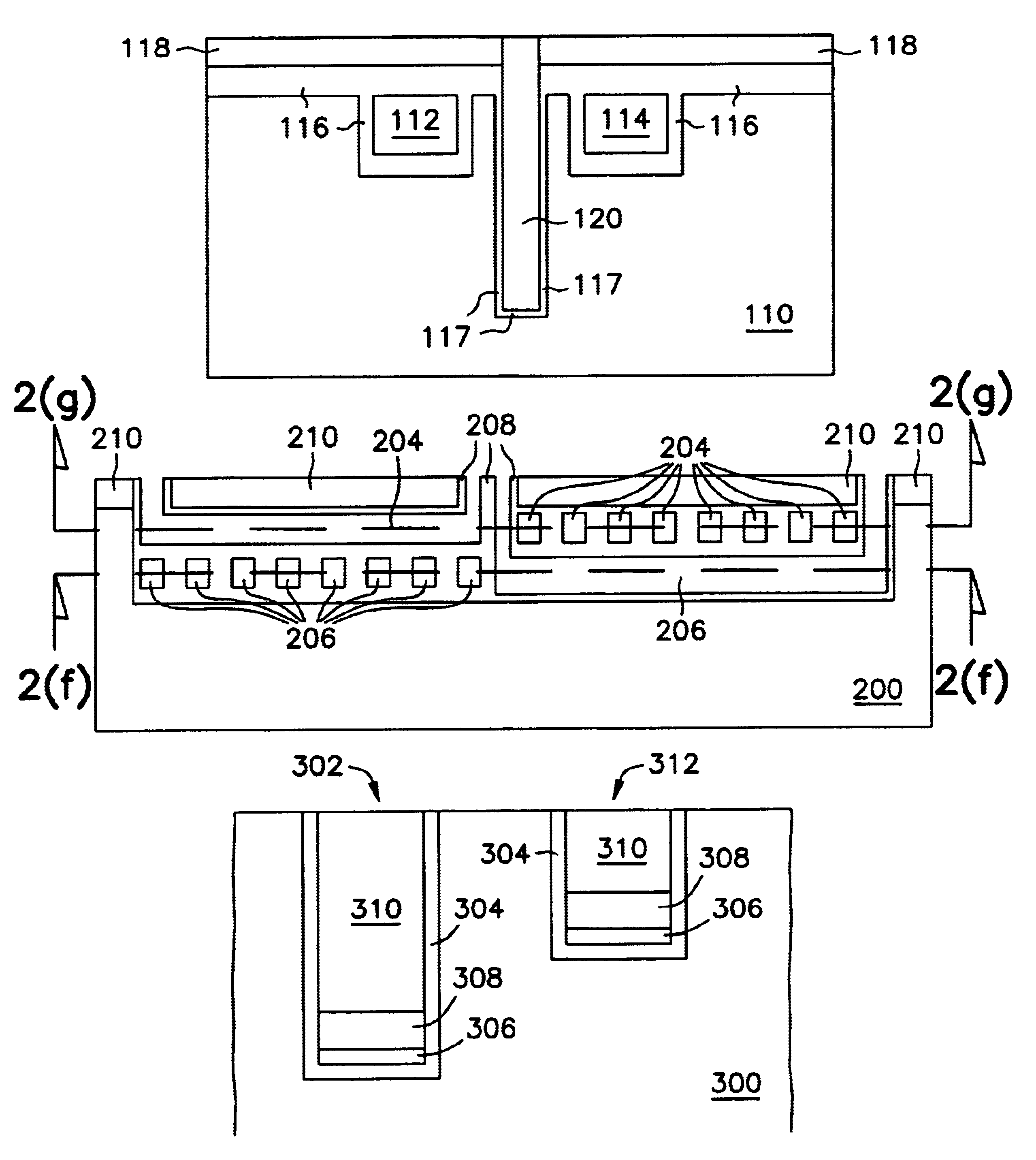

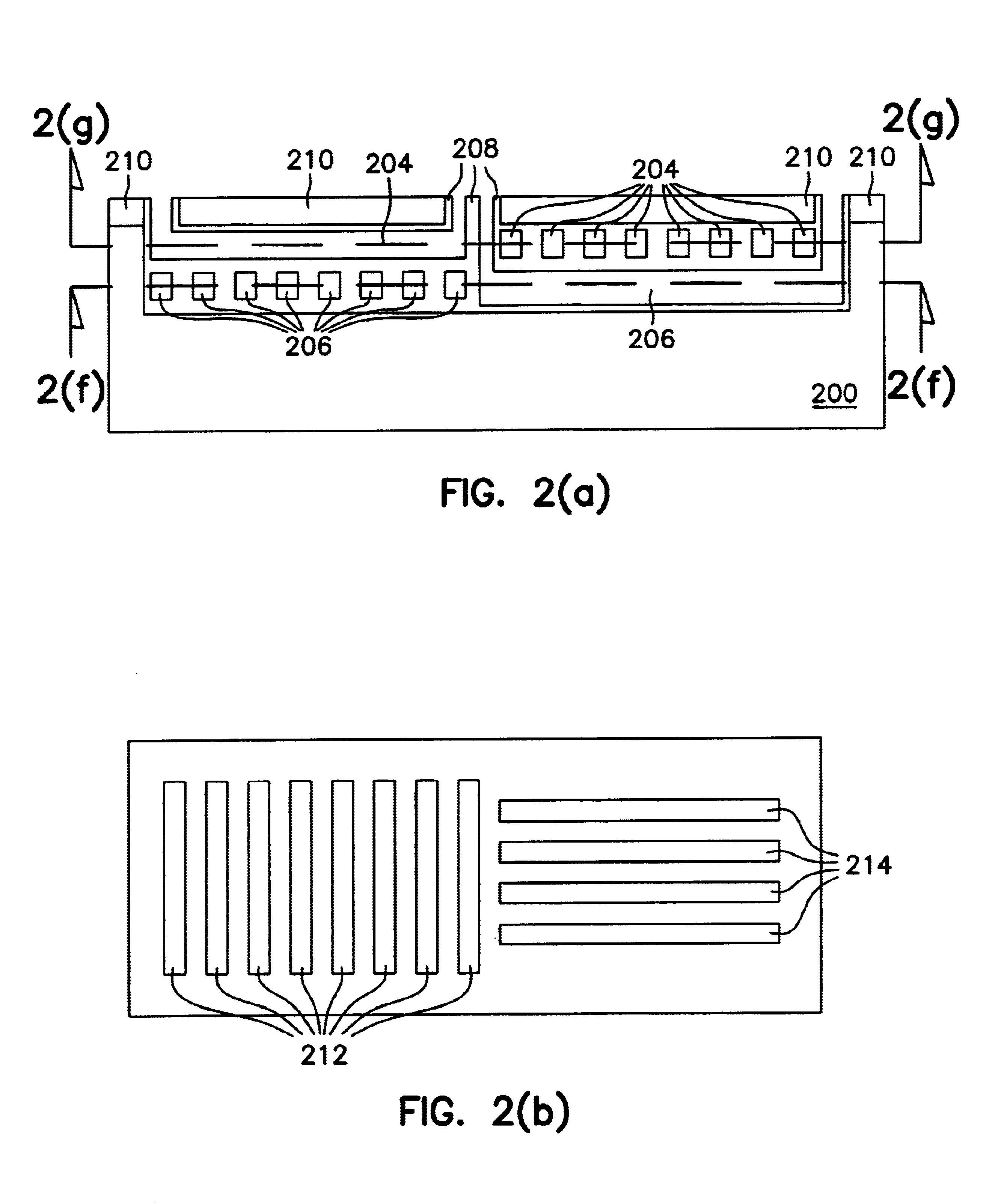

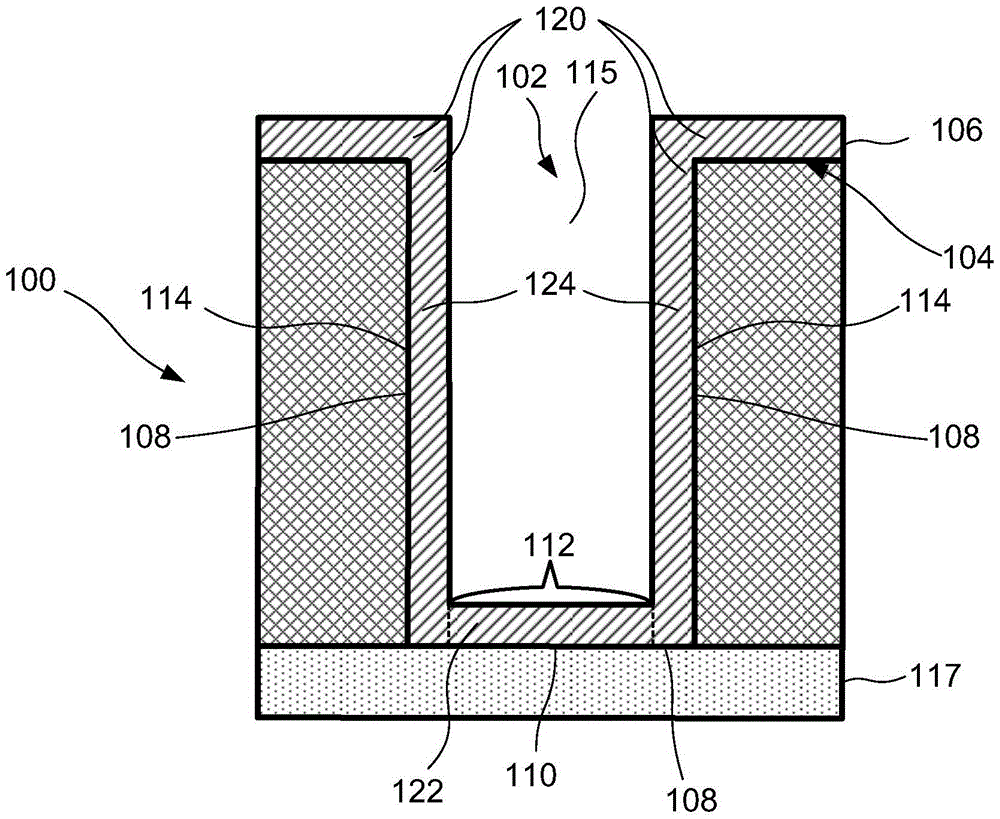

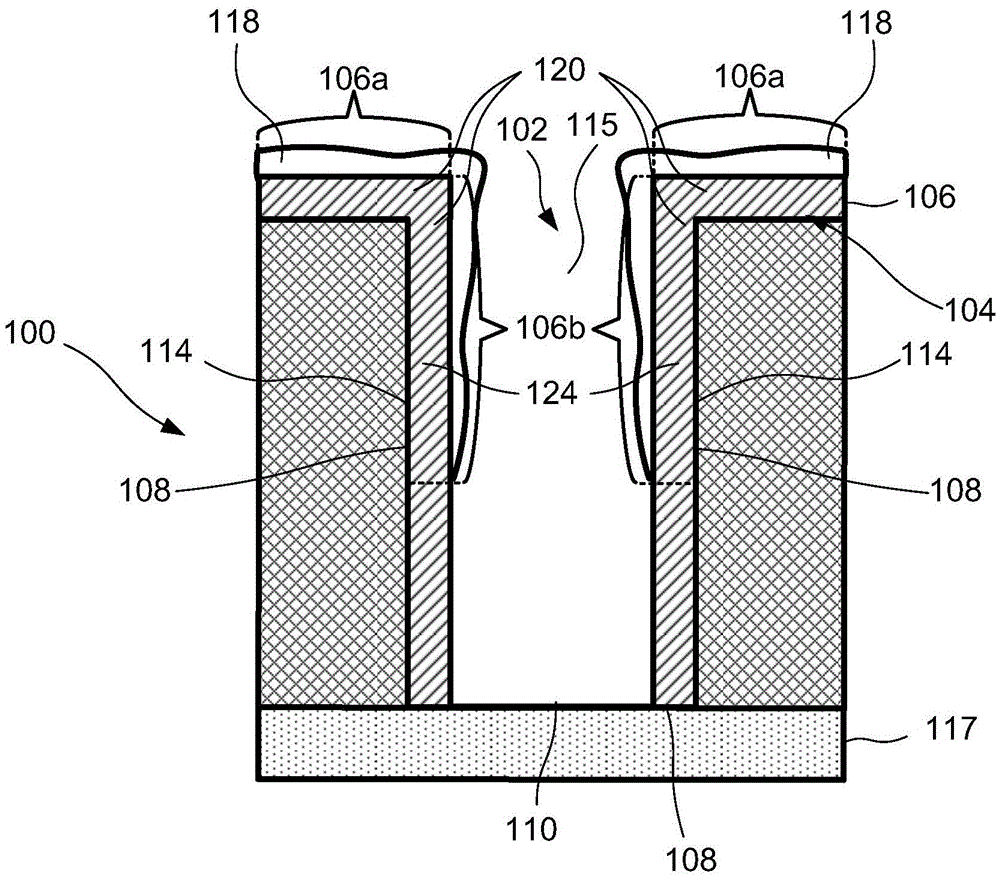

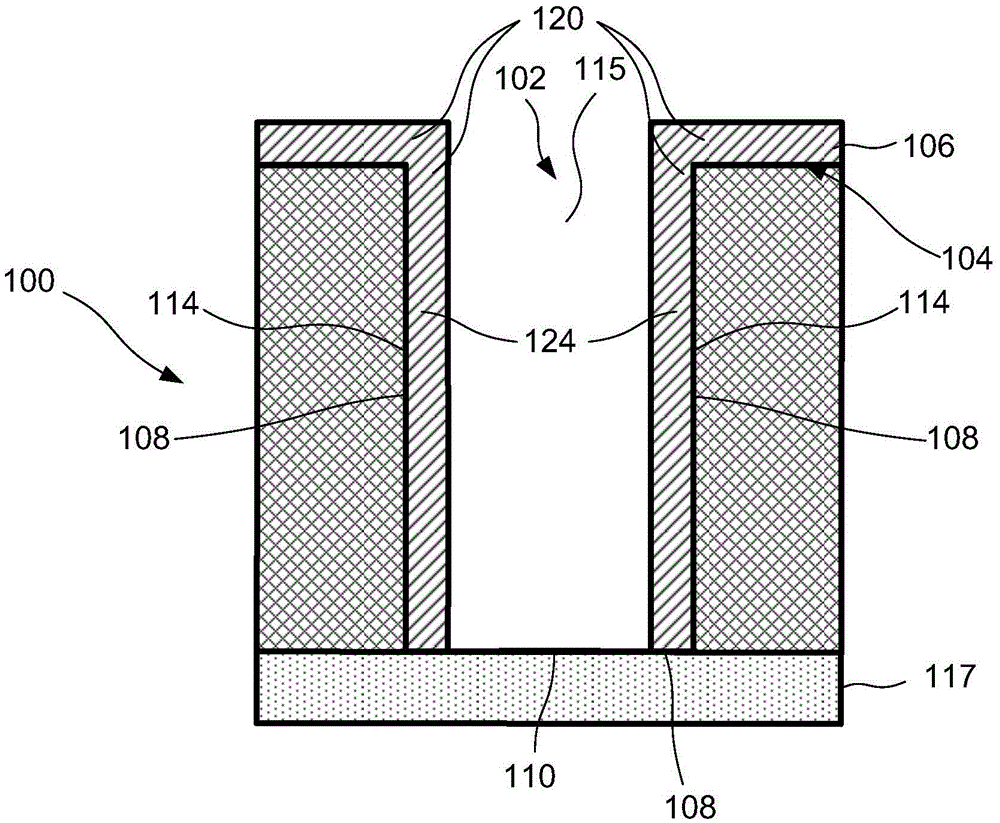

Method of forming buried conductors

InactiveUS6946389B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

Owner:MICRON TECH INC

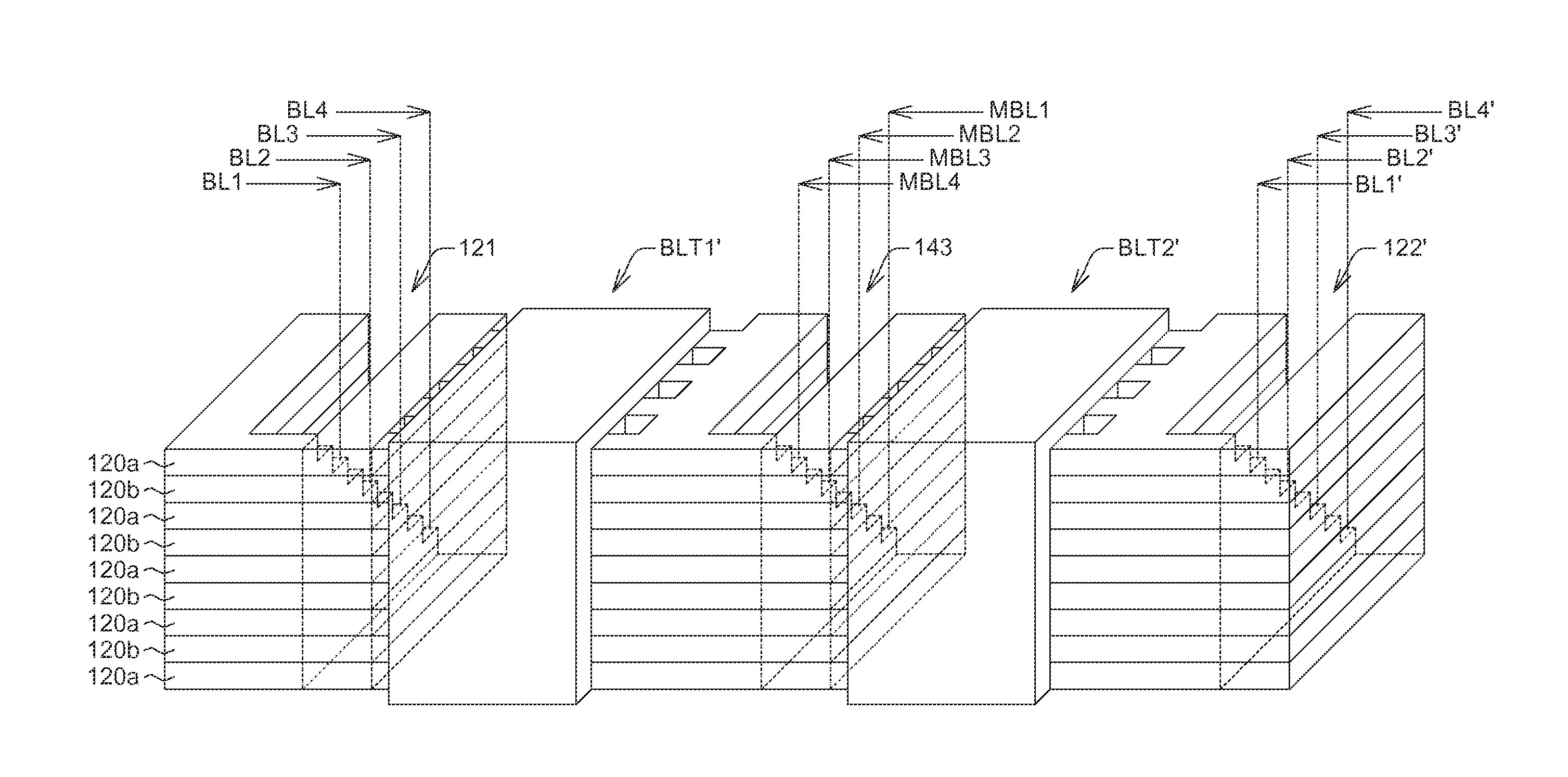

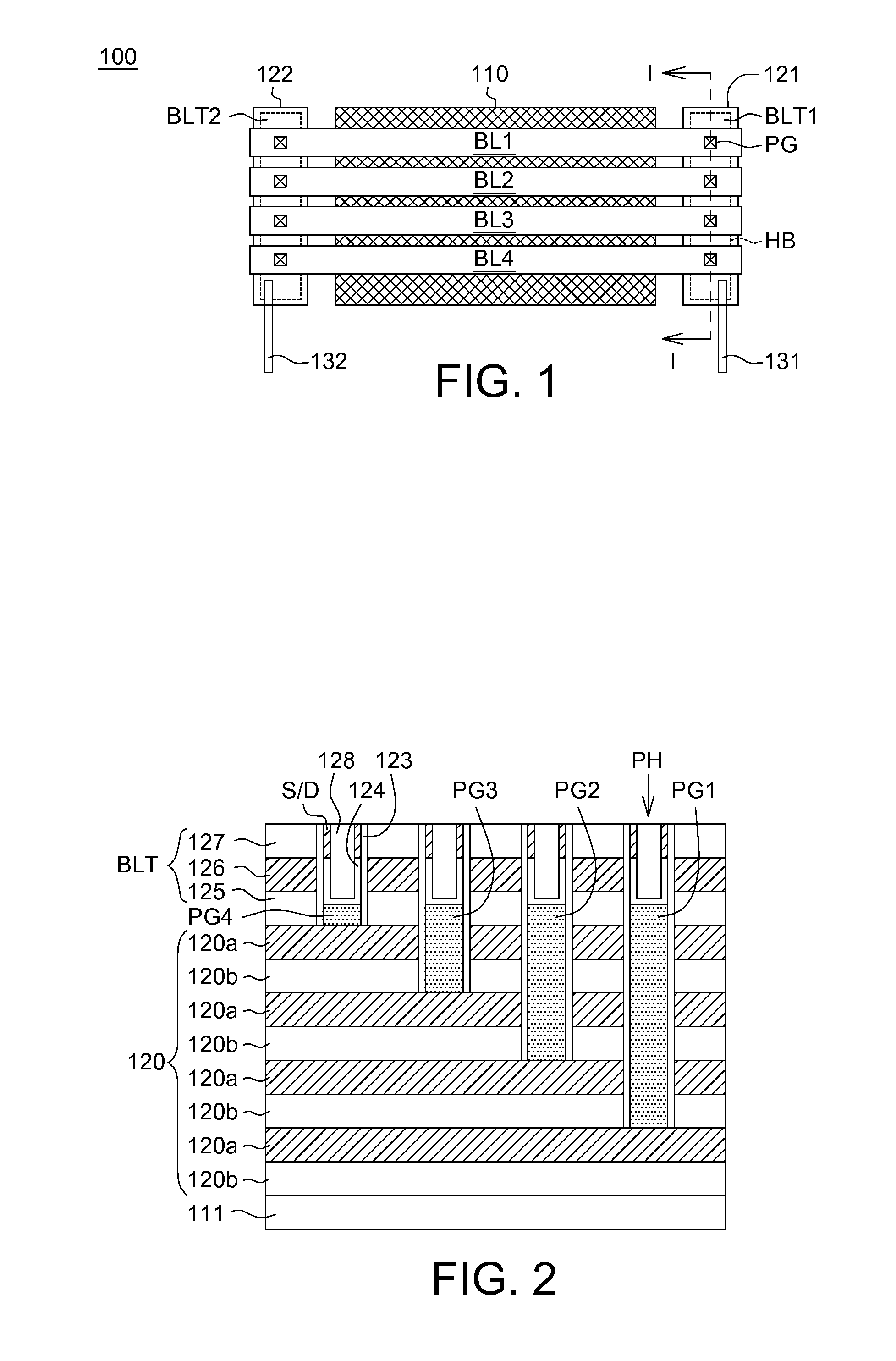

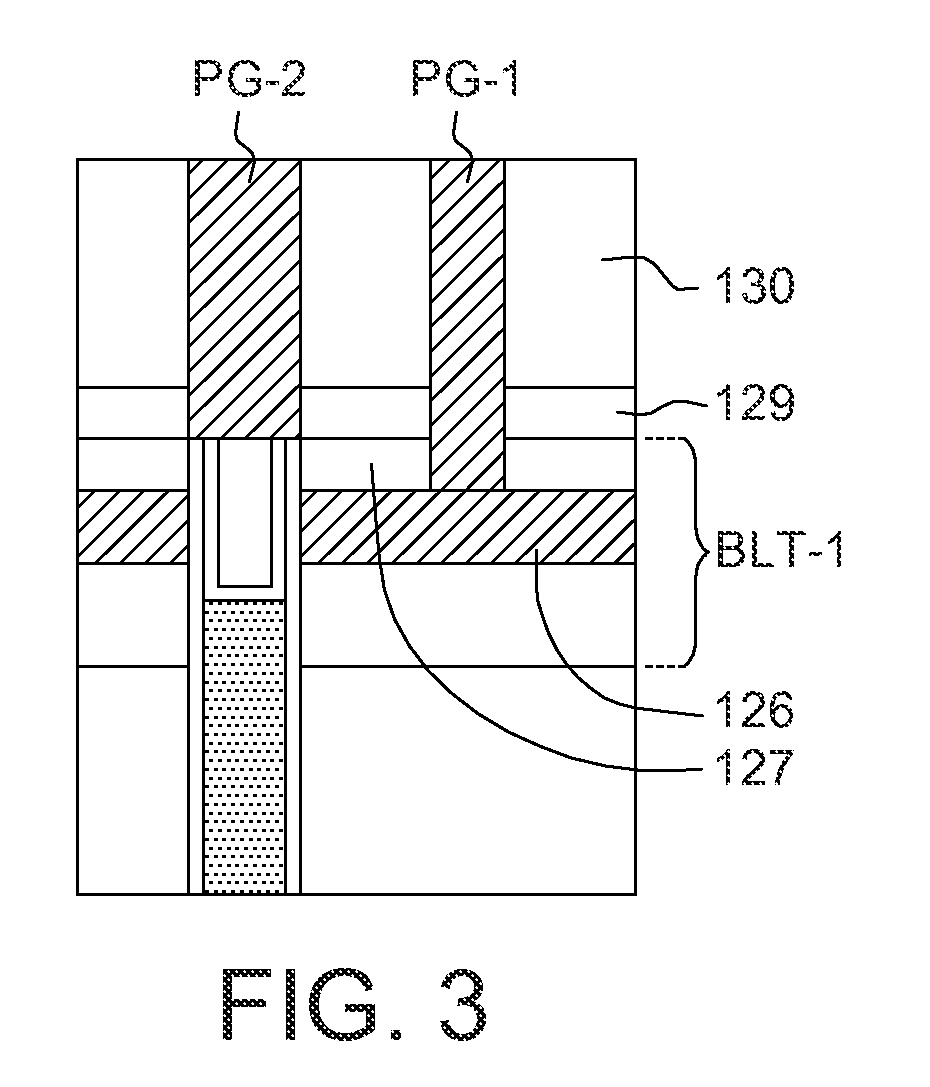

Semiconductor structure with improved capacitance of bit line

ActiveUS20140054535A1Increase capacitanceSignal delayBulk negative resistance effect devicesBit lineCapacitance

Owner:MACRONIX INT CO LTD

Plasma treatment method

ActiveCN105720006ASolid-state devicesSemiconductor/solid-state device manufacturingEtchingSemiconductor structure

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Semiconductor-on-insulator wafer, semiconductor structure including a transistor, and methods for the formation and operation thereof

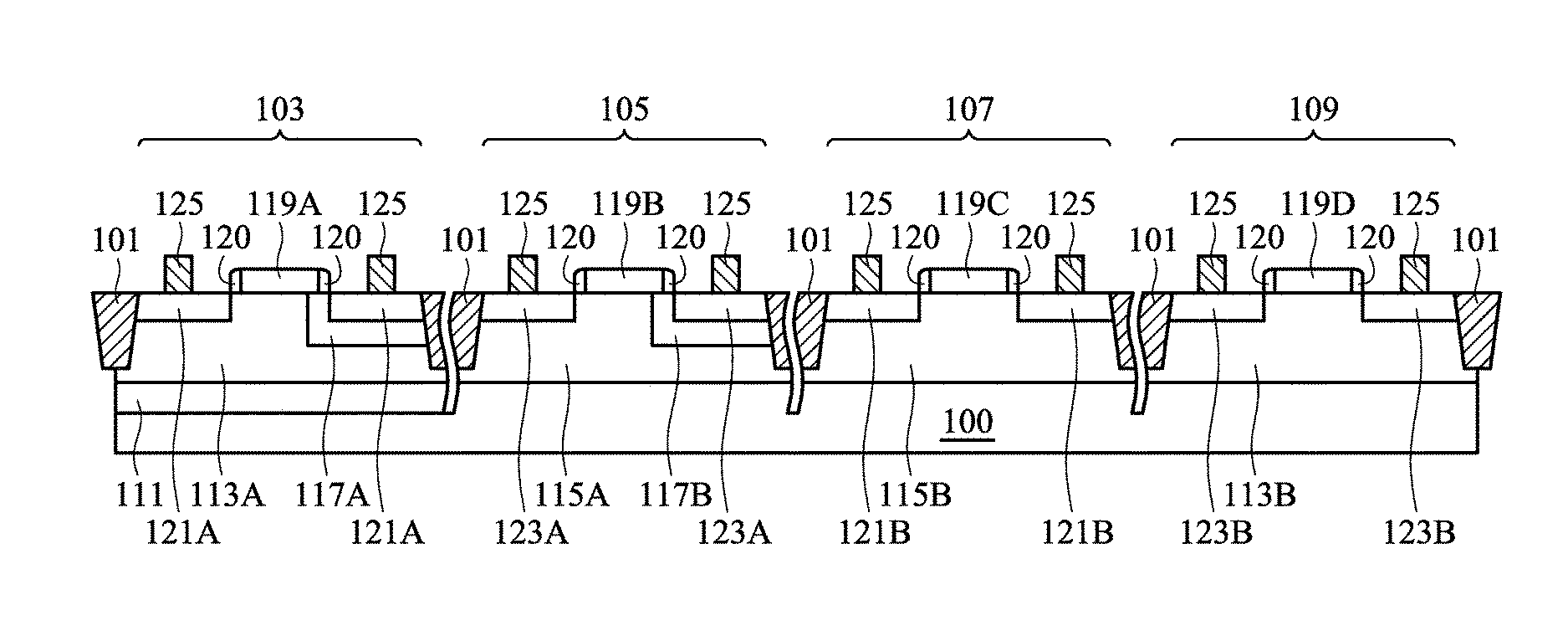

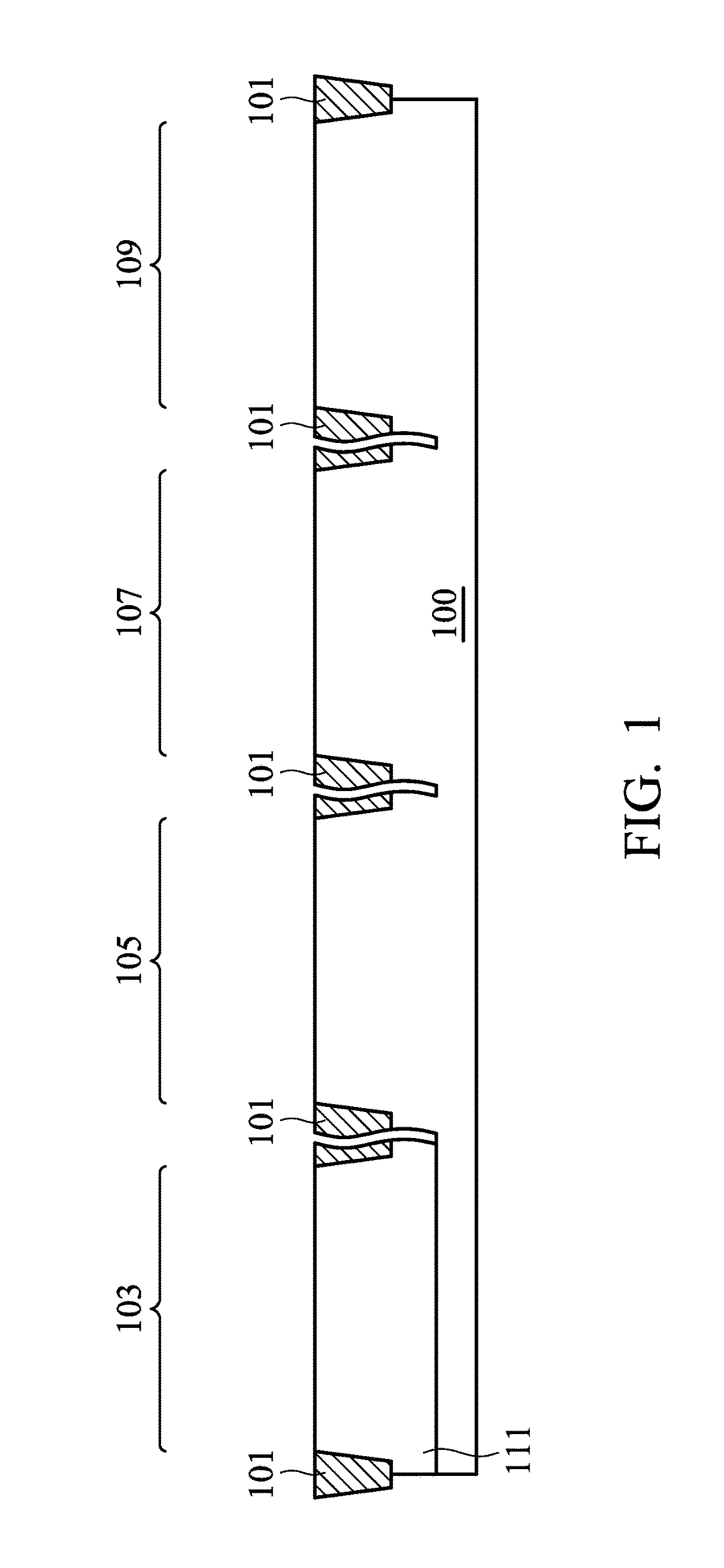

A semiconductor-on-insulator wafer includes a support substrate, an electrically insulating layer over the support substrate and a semiconductor layer over the electrically insulating layer. A semiconductor structure includes a transistor. The transistor includes an electrically insulating layer including a piezoelectric material over a support substrate, a semiconductor layer over the electrically insulating layer, a source region, a channel region and a drain region in the semiconductor layer, a gate structure over the channel region, a first electrode and a second electrode. The first electrode and the second electrode are provided at laterally opposite sides of the electrically insulating layer. The first and second electrodes are electrically insulated from the semiconductor layer and configured for applying a voltage to the piezoelectric material of the electrically insulating layer. The piezoelectric material creates a strain at least in the channel region in response to the voltage applied thereto.

Owner:GLOBALFOUNDRIES U S INC

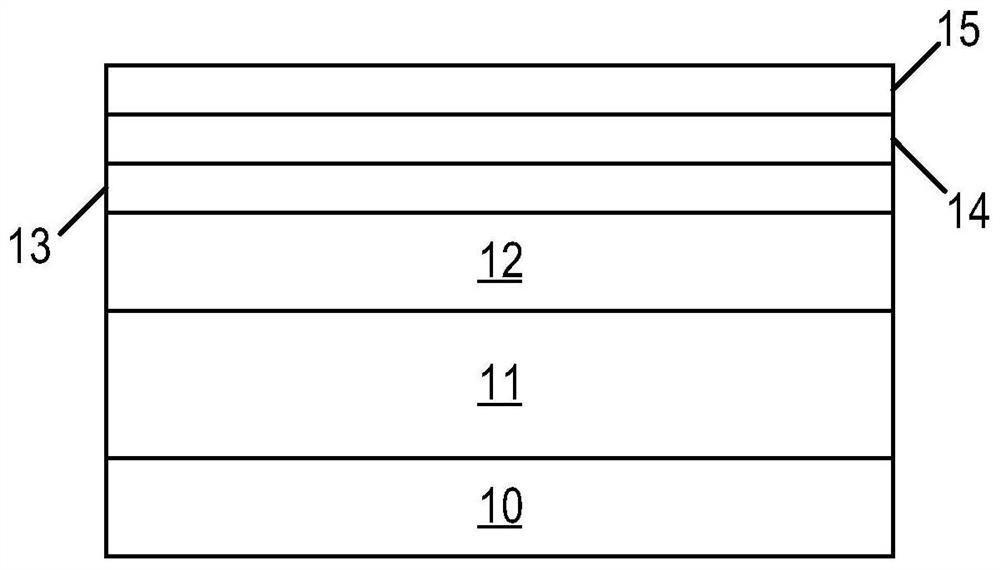

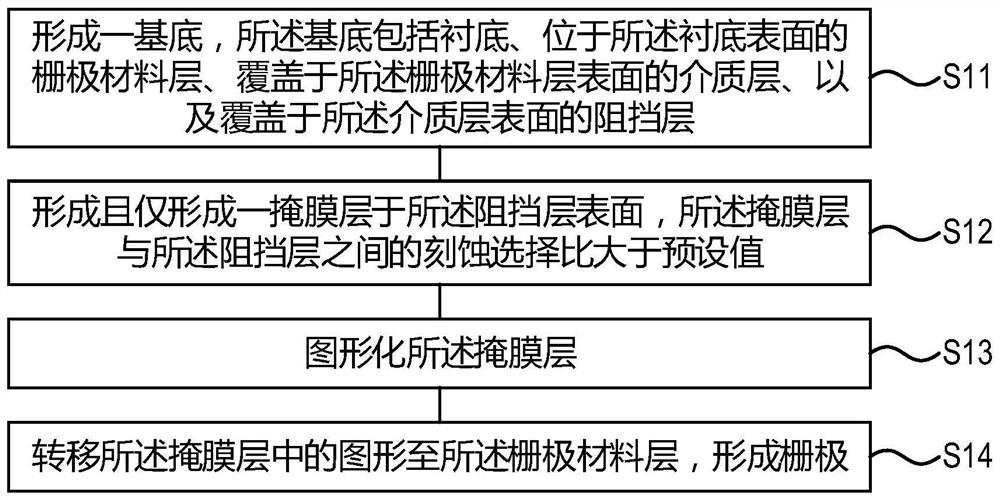

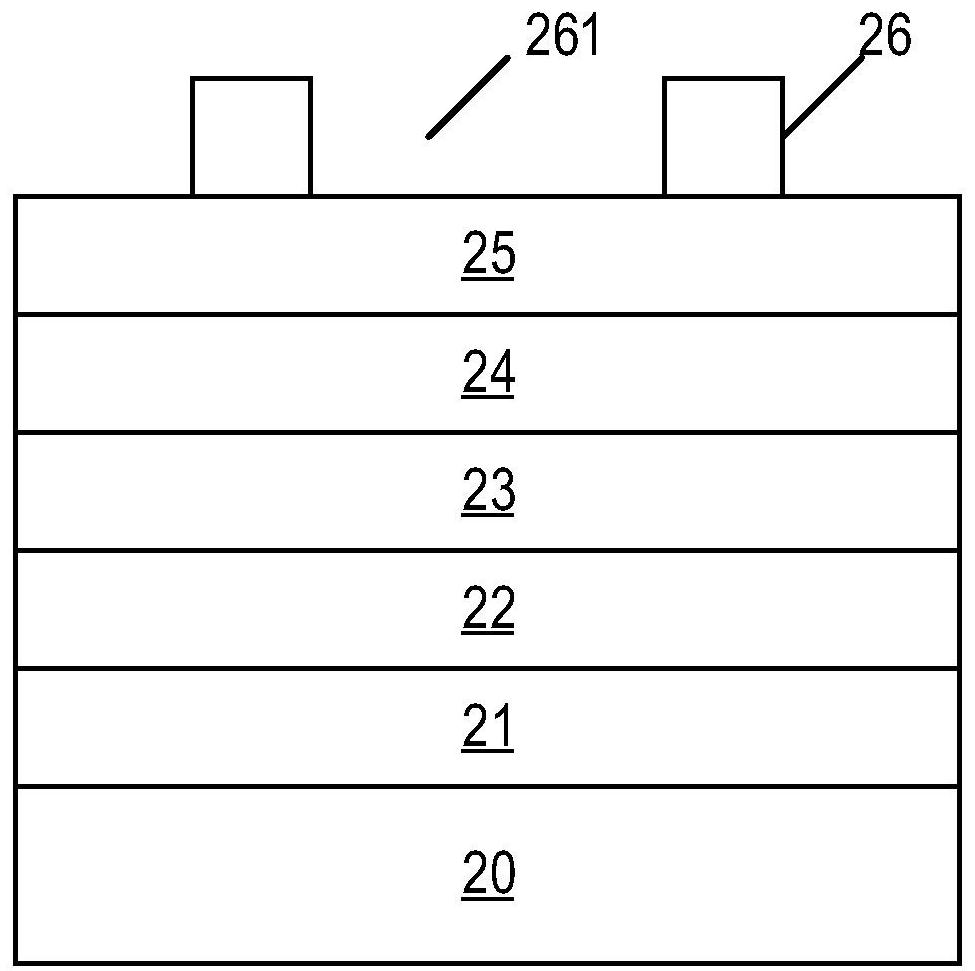

Method for forming gate stack of 3D memory device

ActiveCN110729295AReduce process stepsReduce process complexitySolid-state devicesPhotomechanical apparatusSemiconductor structureIon beam

The invention discloses a method for forming the gate stack of a 3D memory device. The method comprises the following steps that: an insulating stack structure is formed on a semiconductor substrate;a step-shaped mask layer is formed on the insulating laminated structure; a step-shaped insulating laminated structure is formed; and the insulating laminated structure is replaced with a gate laminated structure, and the height of the step-shaped mask layer is set through the material and height of the insulating laminated structure. According to the method of the invention, a gray-scale photoetching method, a nanoimprint lithography method, a gray-scale mask plate photoetching method or an ion beam gas-assisted deposition method is adopted to form a step-shaped mask layer; a semiconductor structure is etched by using dry etching, so that the pattern of the mask layer is transferred into the insulating laminated structure; and therefore, process steps are reduced, and process complexity is reduced.

Owner:SHANGHAI IND U TECH RES INST

Method for simulating electrical property of wafer chip and semiconductor process method

PendingCN114823398ARealize electrical evaluationTimely detection of electrical abnormalitiesSemiconductor/solid-state device testing/measurementSemiconductor structureComputational physics

The invention relates to a method for simulating the electrical property of a wafer chip, and the method is characterized in that the method comprises the steps: constructing a database, the database comprises spectral data of a semiconductor structure obtained after a wafer chip is subjected to a target key process, actual electrical data of the wafer chip and a corresponding relation between the spectral data and the actual electrical data; the target key process is executed on a target wafer chip, spectral data of a semiconductor structure obtained after the target wafer chip is subjected to the target key process are obtained, and the spectral data are target spectral data; and simulating electrical data of the target wafer chip based on the acquired target spectral data and the database, wherein the electrical data is target electrical data. According to the method for simulating the electrical property of the wafer chip, the electrical property parameters of the wafer chip can be evaluated in time after the target key process, electrical property abnormity occurring in the preparation process of the wafer chip can be found in time, and waste of manpower, material resources and financial resources is reduced.

Owner:CHANGXIN MEMORY TECH INC

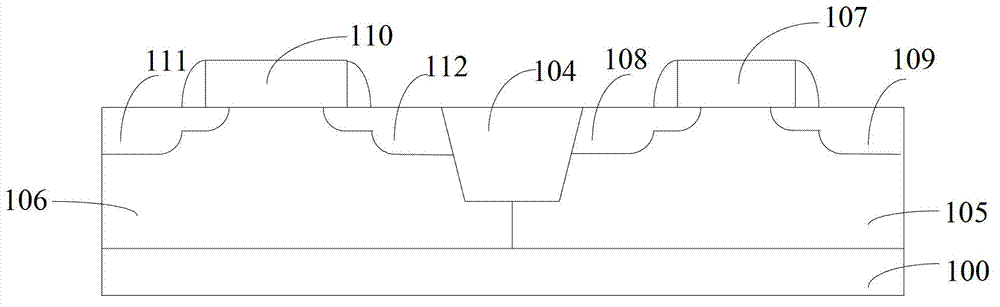

Semiconductor structure having a high voltage well region

ActiveUS20190229206A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureHigh voltage

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

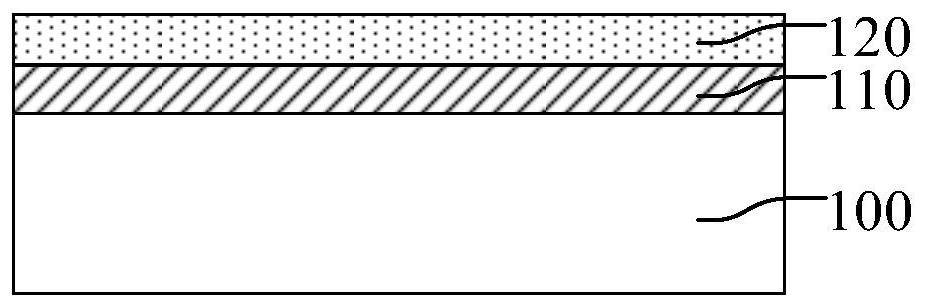

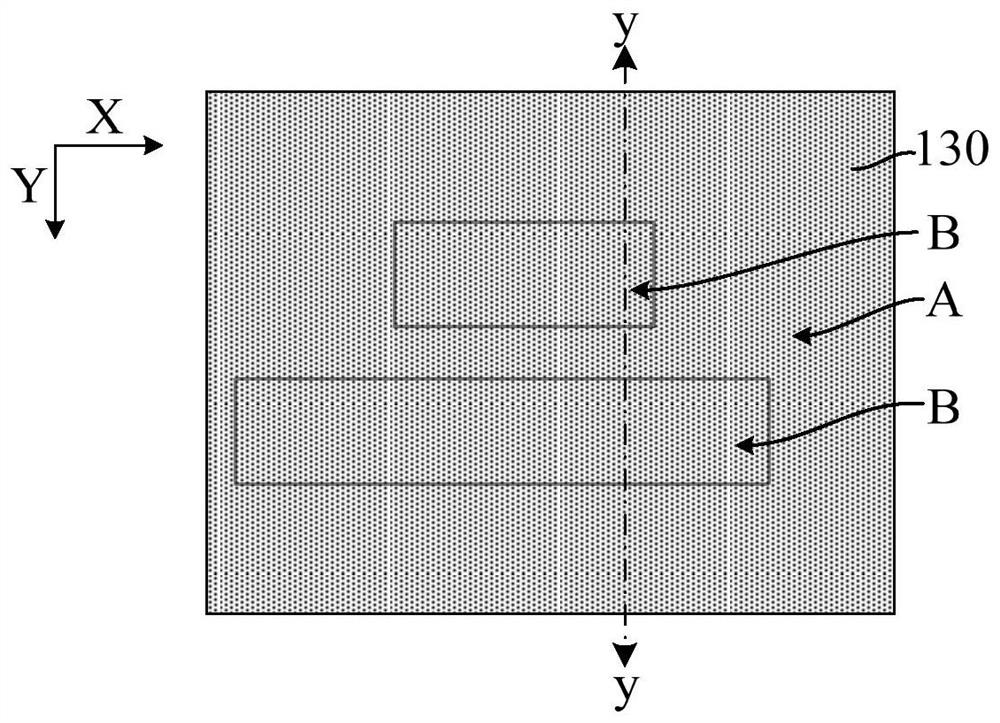

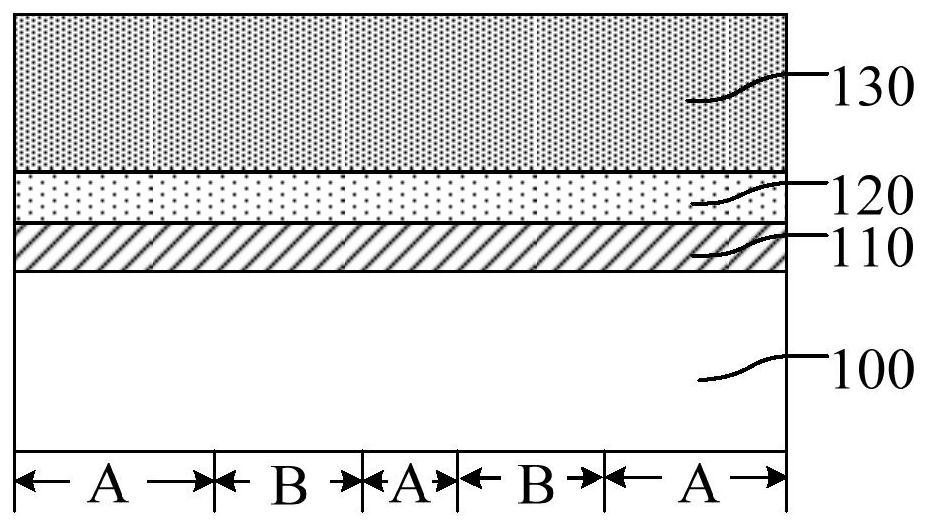

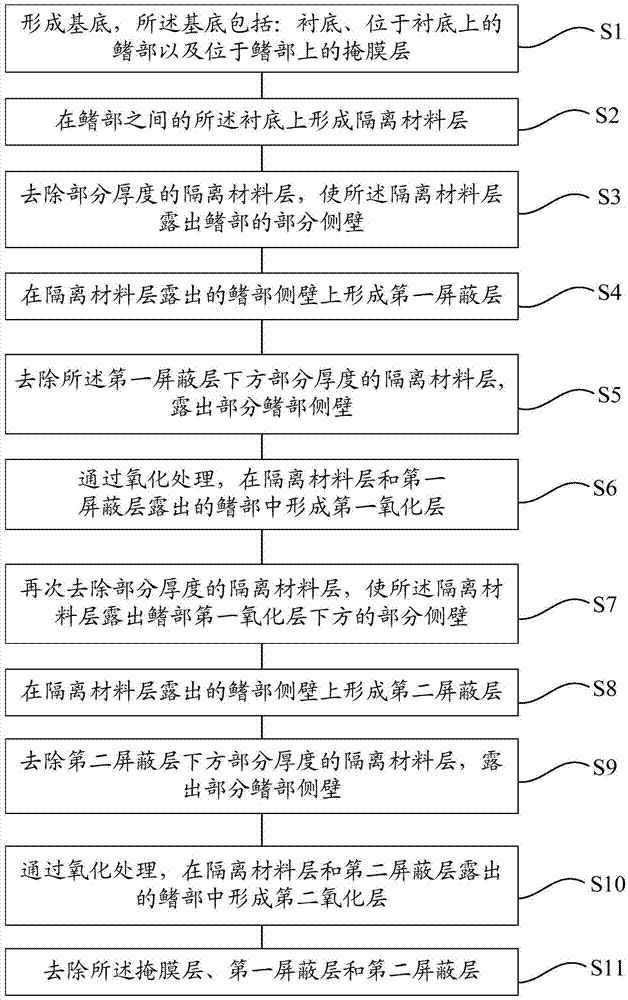

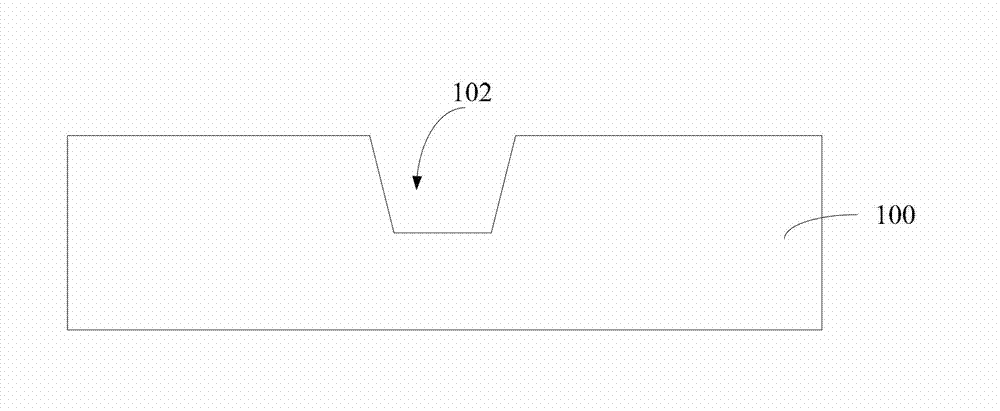

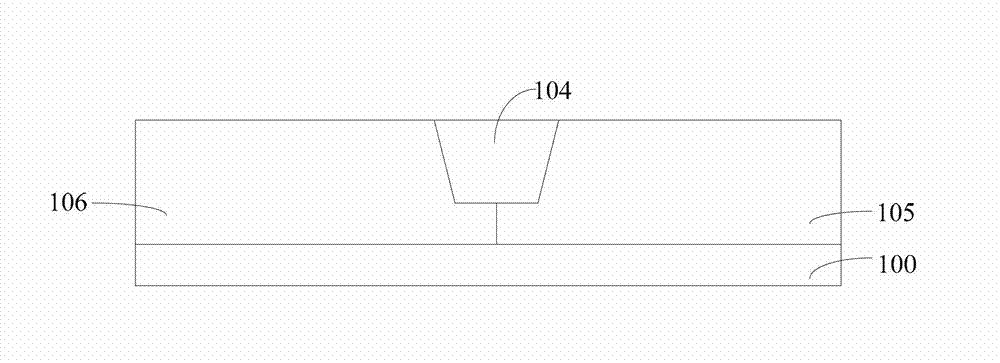

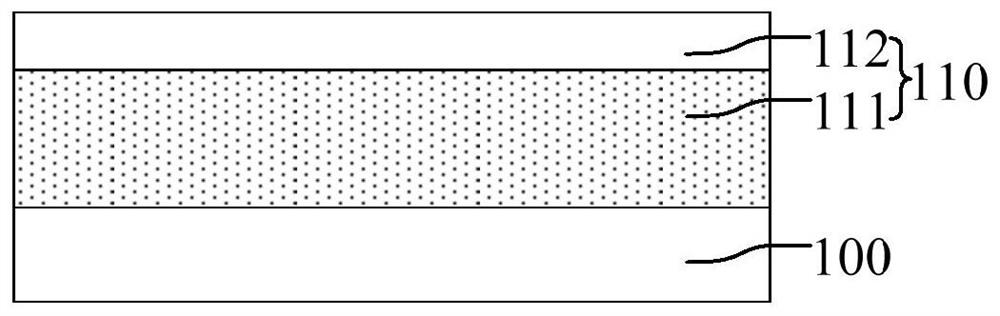

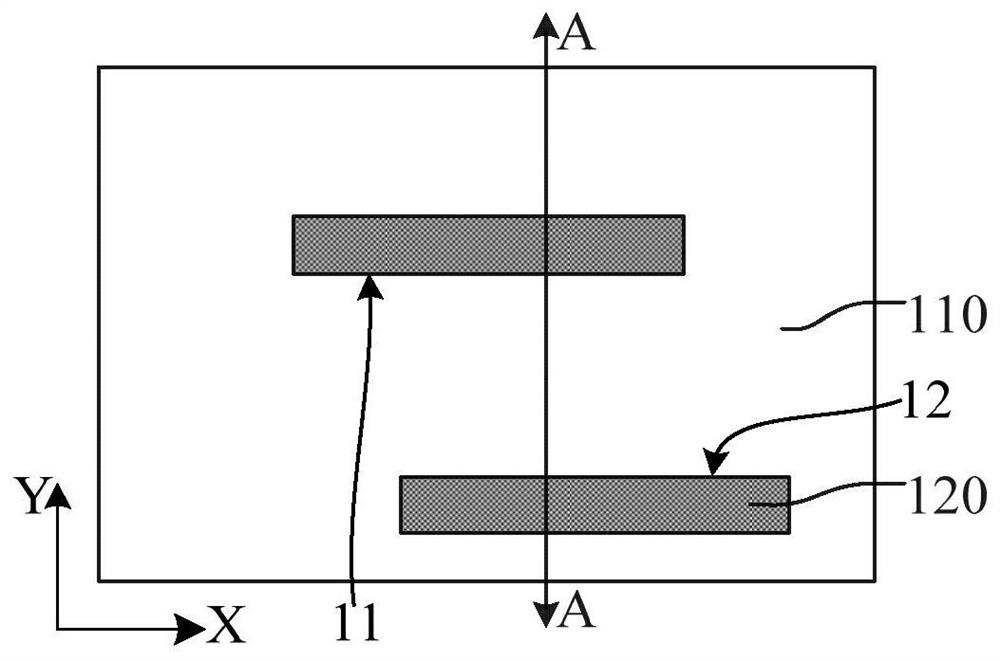

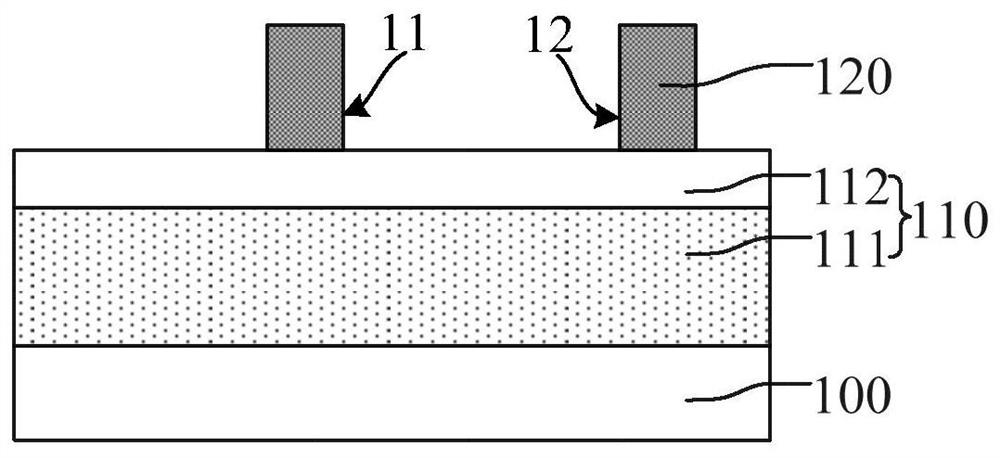

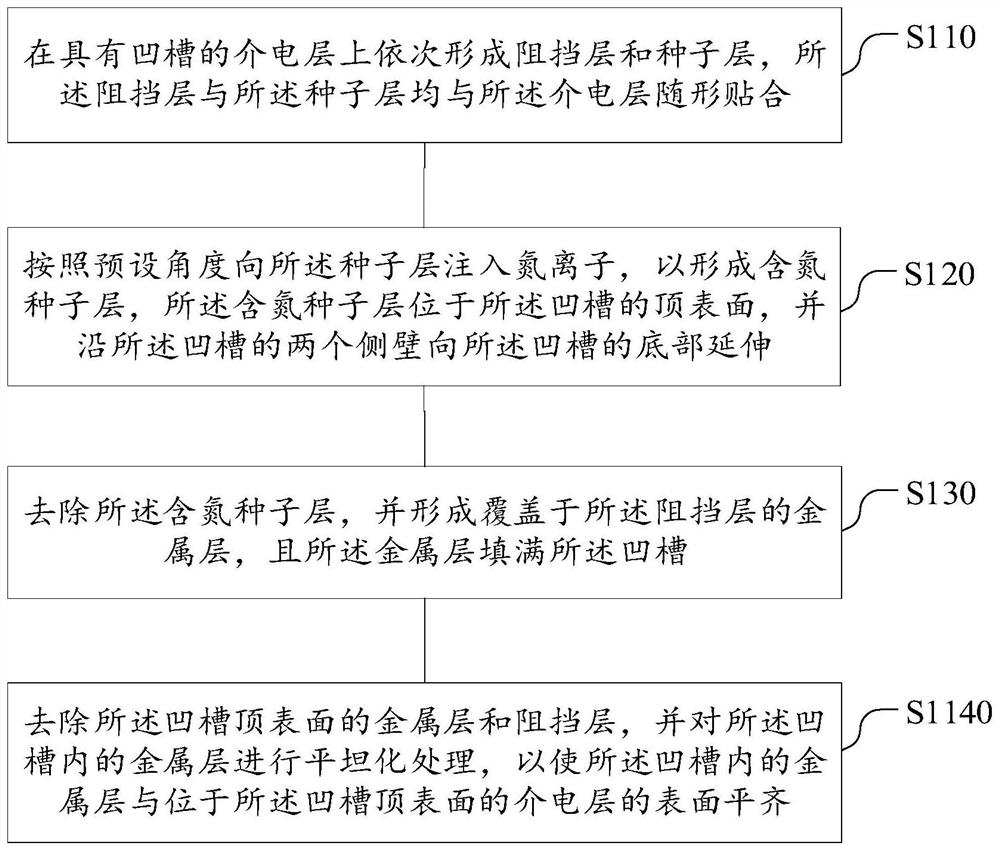

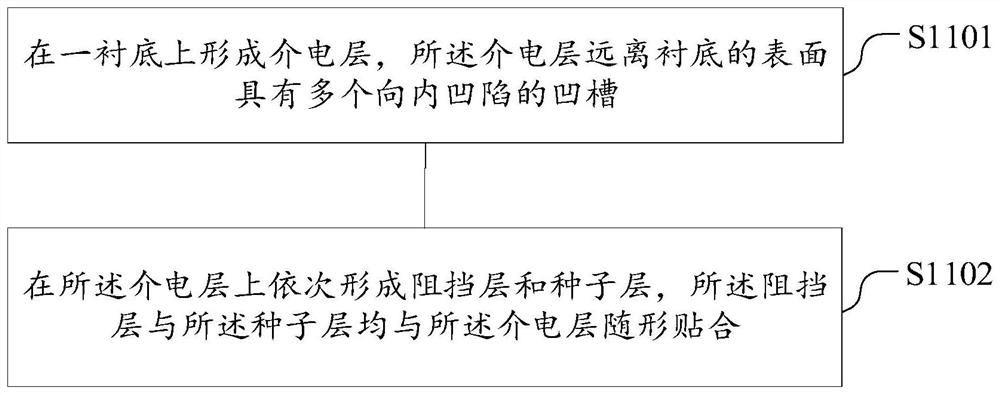

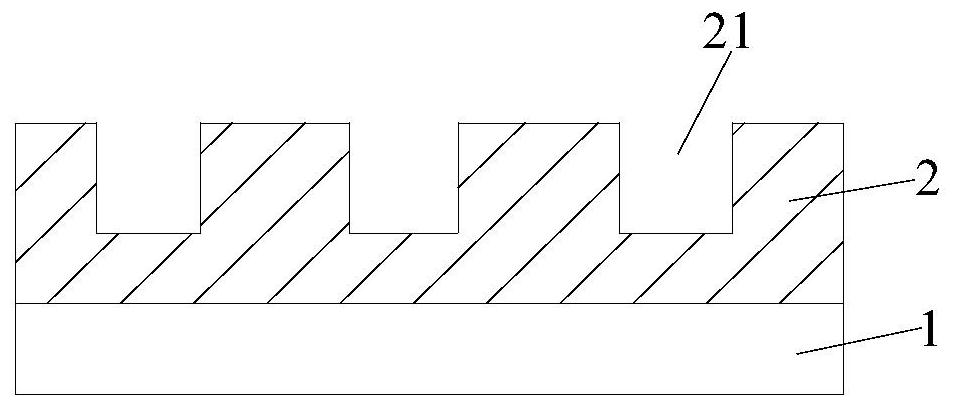

Method for manufacturing semiconductor structure

ActiveCN103295955AAvoid inaccuraciesImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor structureMedia layer

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor structure and method for manufacturing the same

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Semiconductor structure and semiconductor device

PendingCN114171483AAffect the subsequent processAffect the test effectSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDevice material

Owner:WUHAN XINXIN SEMICON MFG CO LTD

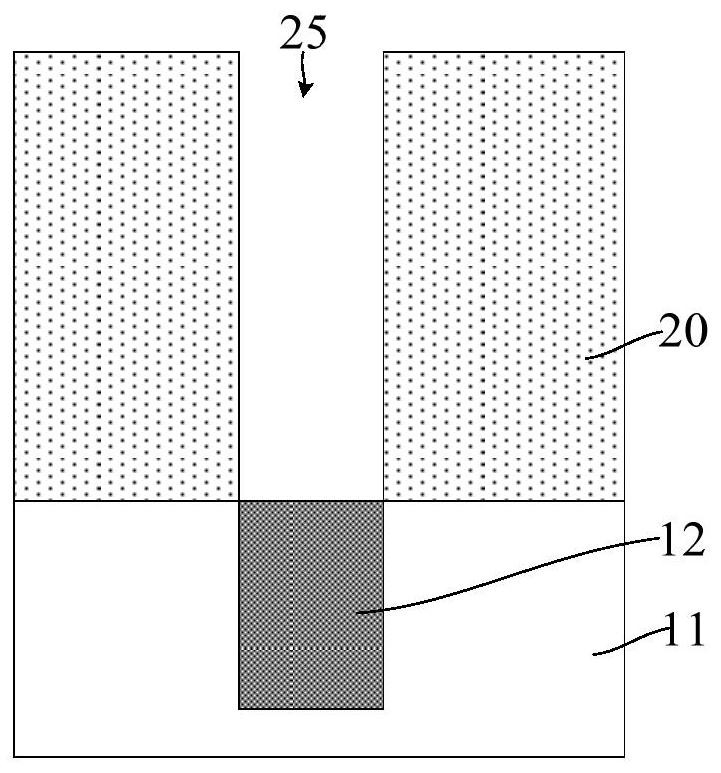

Formation method of semiconductor structure

PendingCN114551333AReduce difficultyImprove process controlSolid-state devicesSemiconductor/solid-state device manufacturingCrystallographySemiconductor structure

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

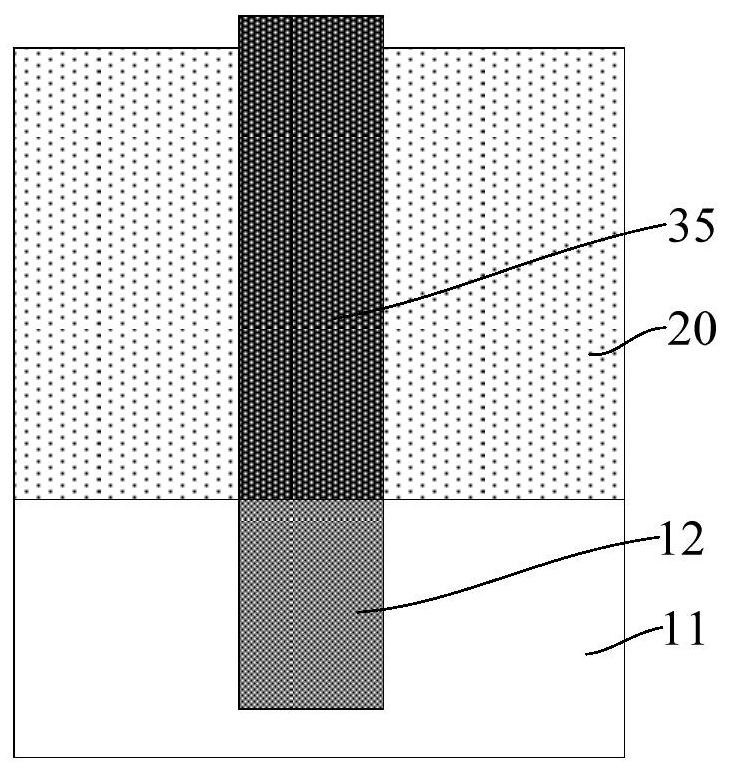

Formation method of semiconductor structure

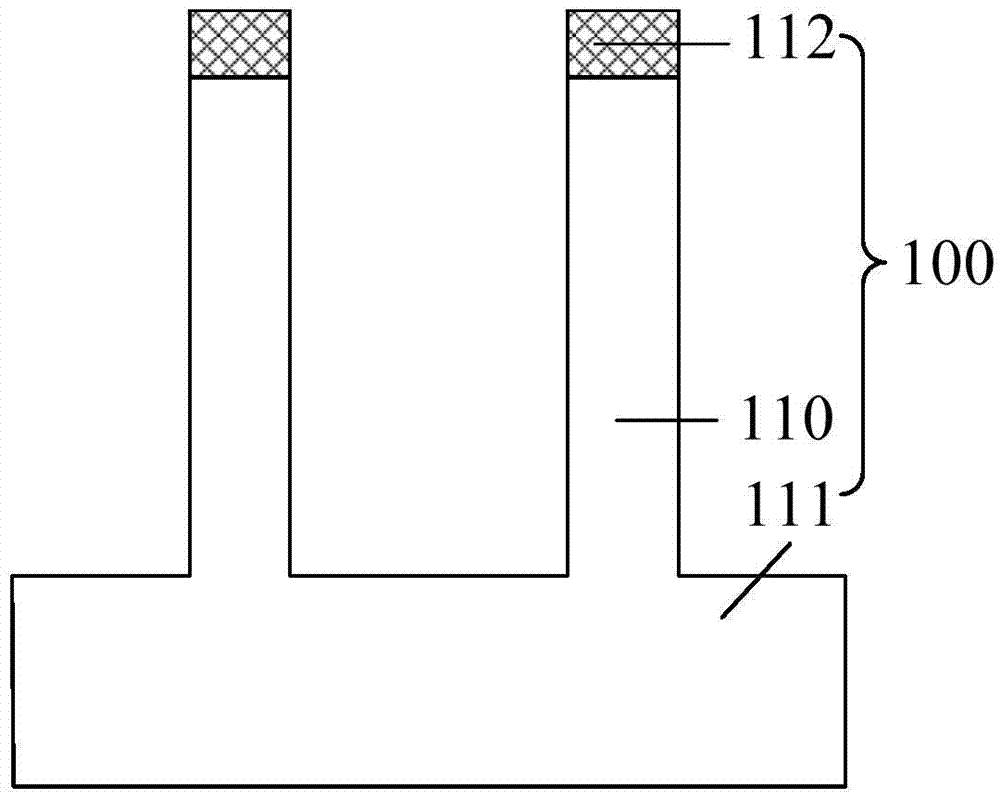

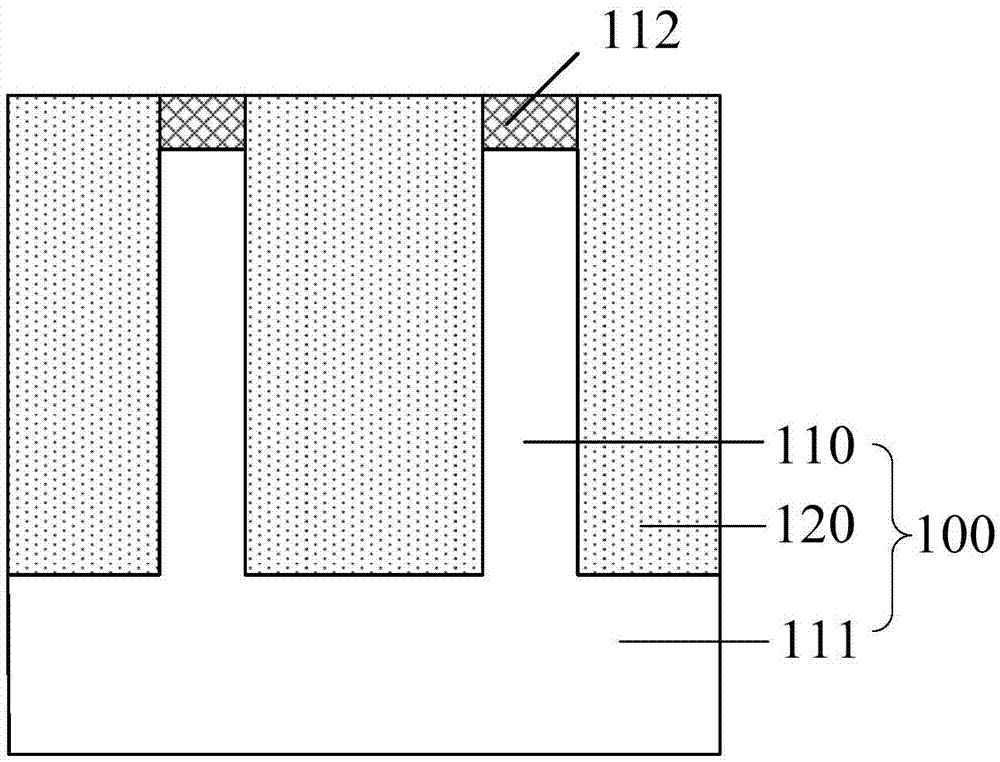

InactiveCN106952814AImprove uniformityImprove compactnessSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

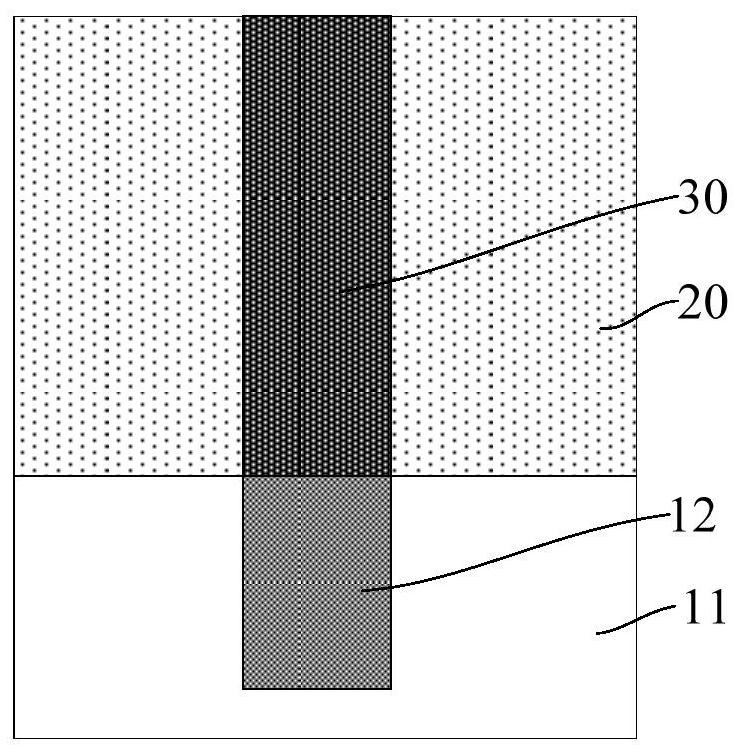

Forming method of semiconductor structure, and semiconductor structure

InactiveCN103928384ASemiconductor/solid-state device manufacturingEngineeringSemiconductor structure

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor structure and forming method thereof

PendingCN112825308AImprove formation qualityReduce the impactSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and forming method thereof

PendingCN113948462AIncreased freedom in graphic designIncrease flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureStructural engineering

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device, semiconductor structure and manufacturing method of interconnection structure

InactiveCN112530856AAvoid gatheringPrevent proliferationSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDevice material

Owner:CHANGXIN MEMORY TECH INC

Semiconductor structure and forming method thereof

ActiveCN112864096AImprove formation efficiencyReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

Owner:CHANGXIN MEMORY TECH INC

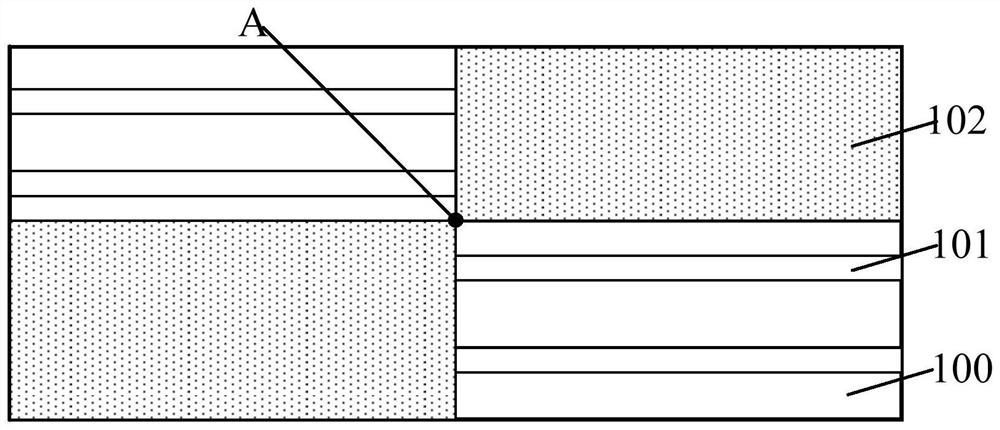

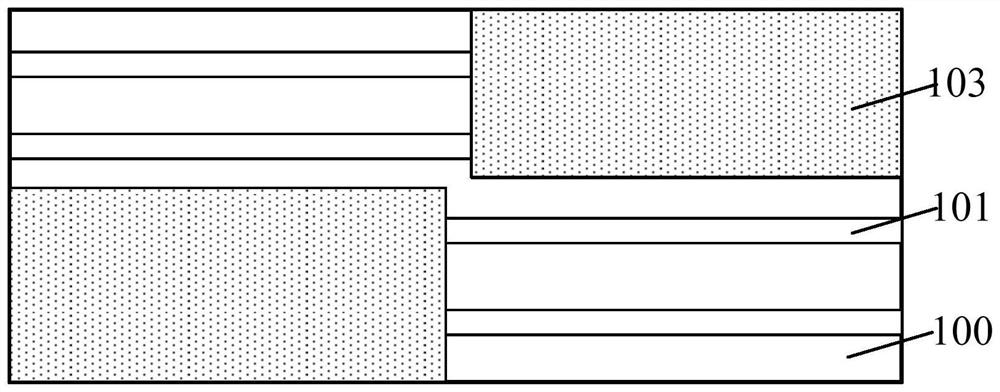

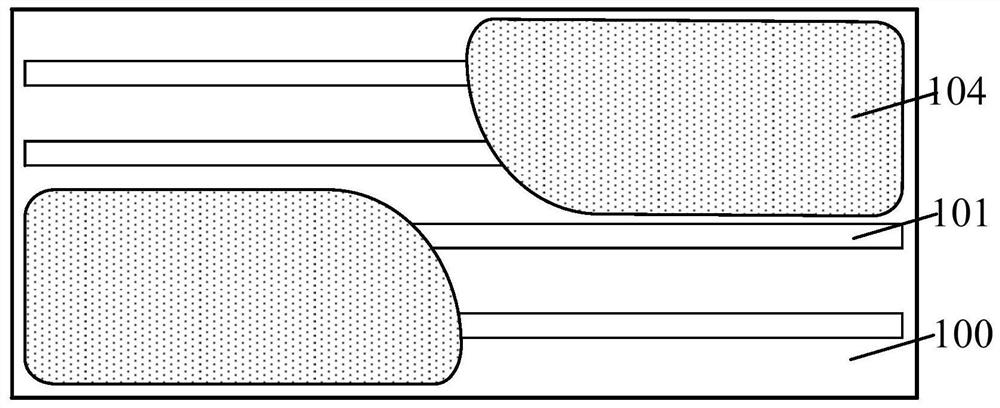

Pattern correction method and semiconductor structure forming method

PendingCN114063380ASmooth structure edgesSmall sizeSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSemiconductor structureEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

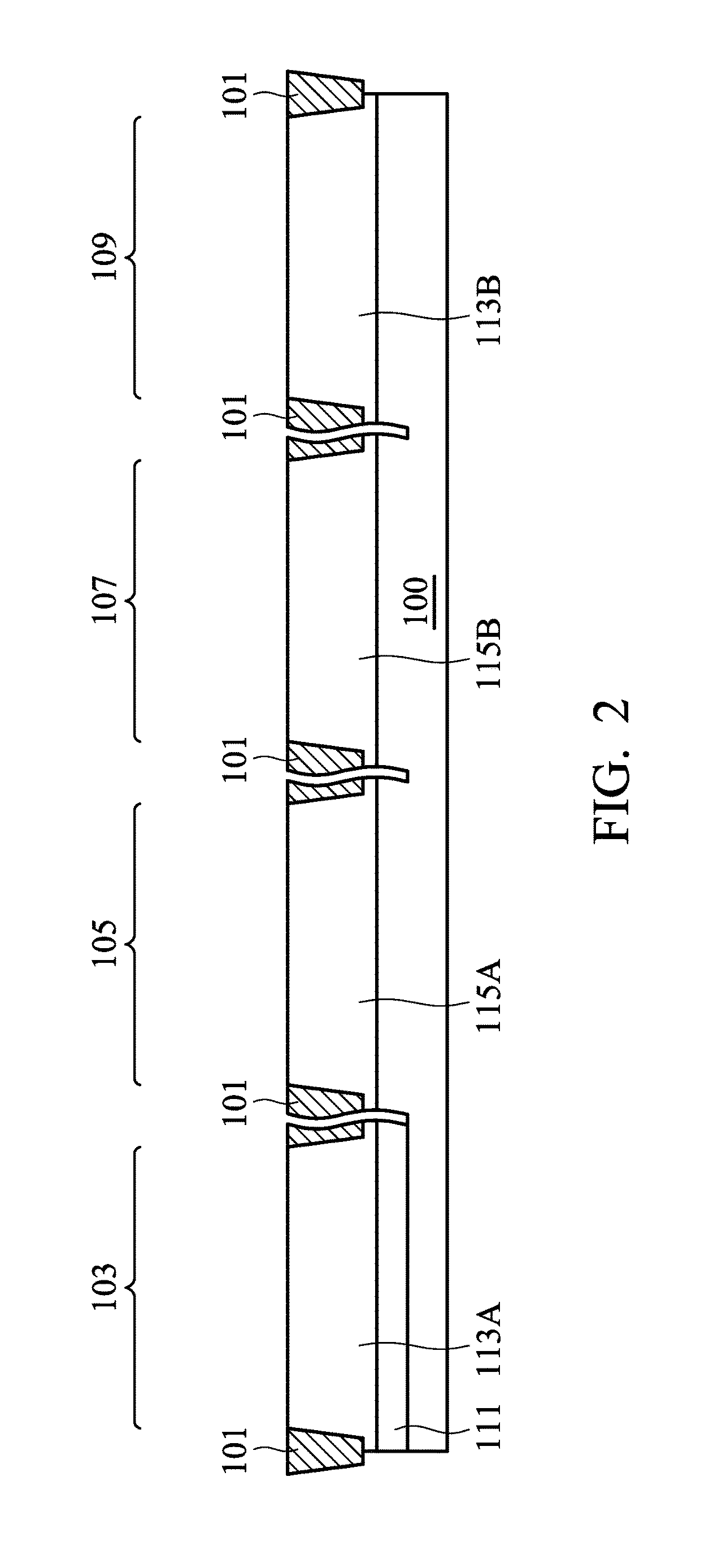

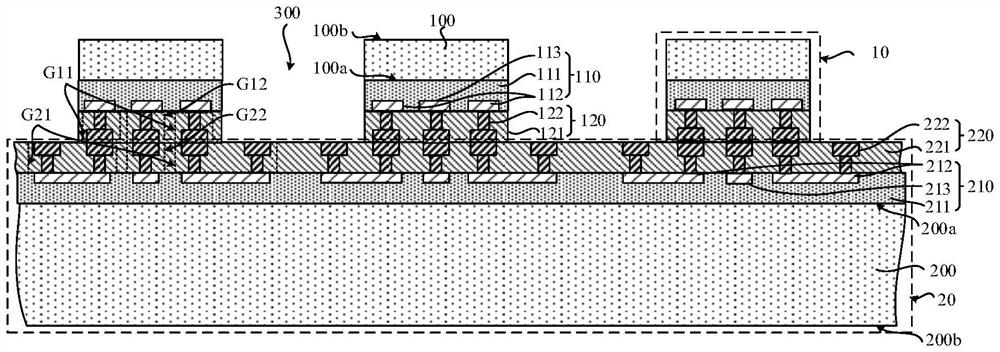

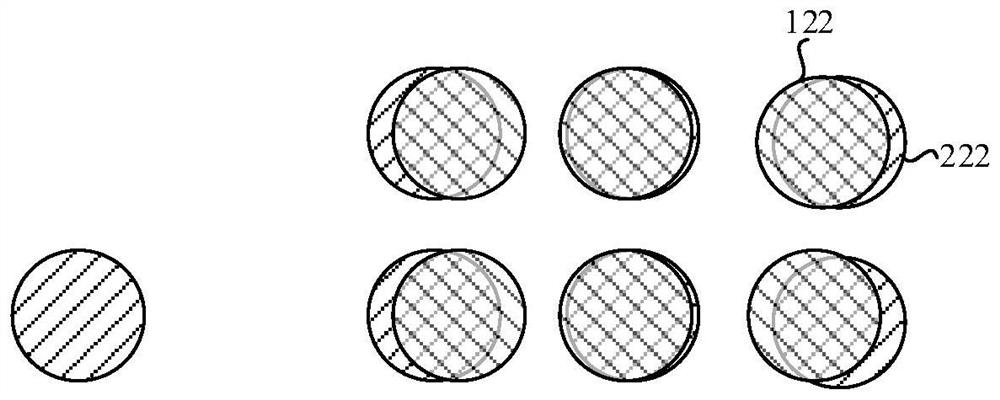

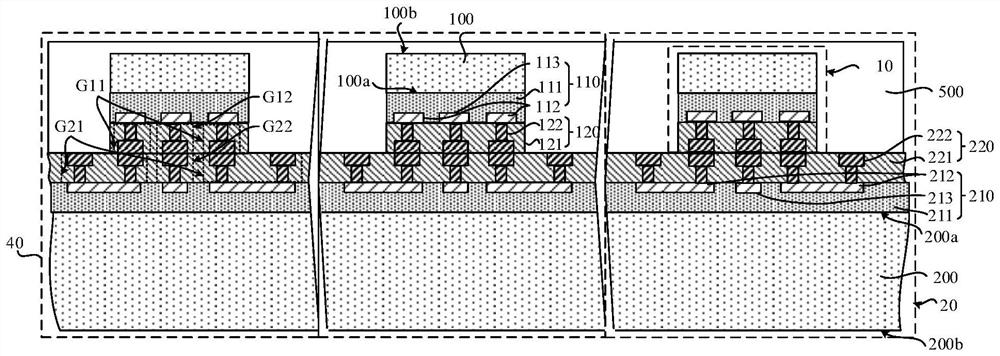

Semiconductor structure and manufacturing method thereof

PendingCN113013112AAchieve electrical connectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureElectrical connection

Owner:ADVANCED SEMICON ENG INC

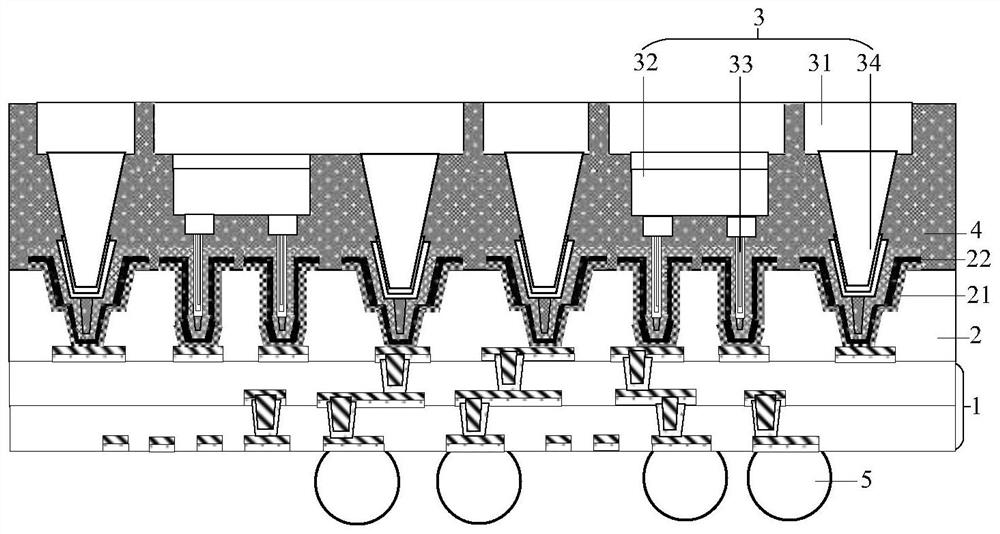

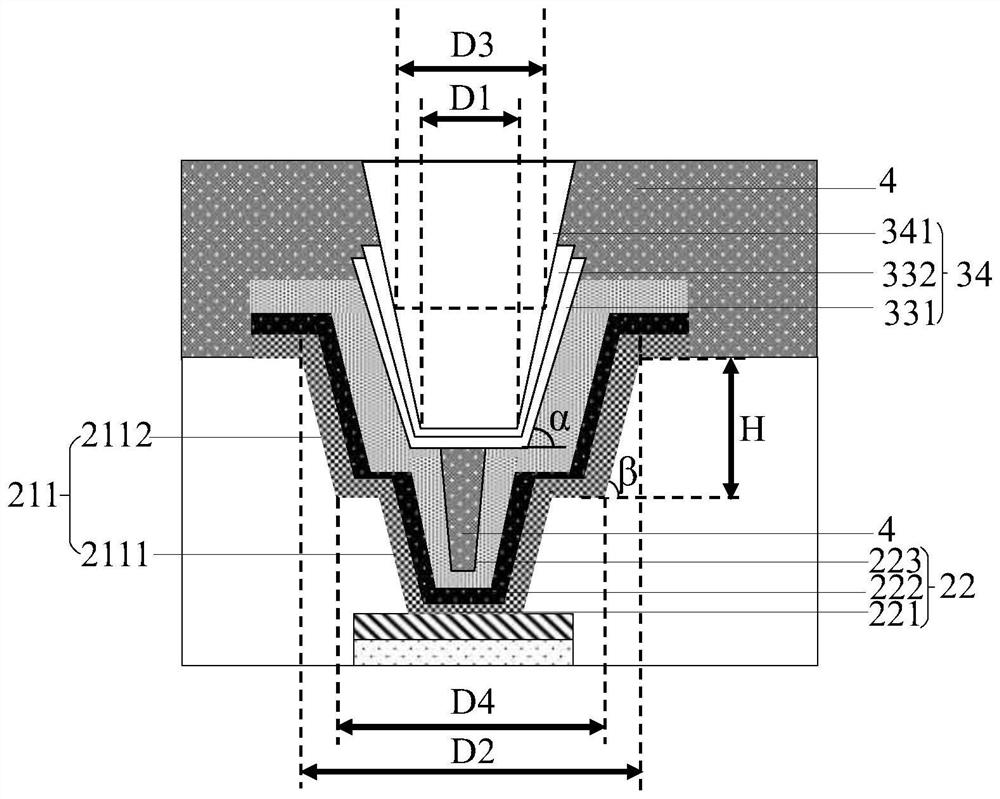

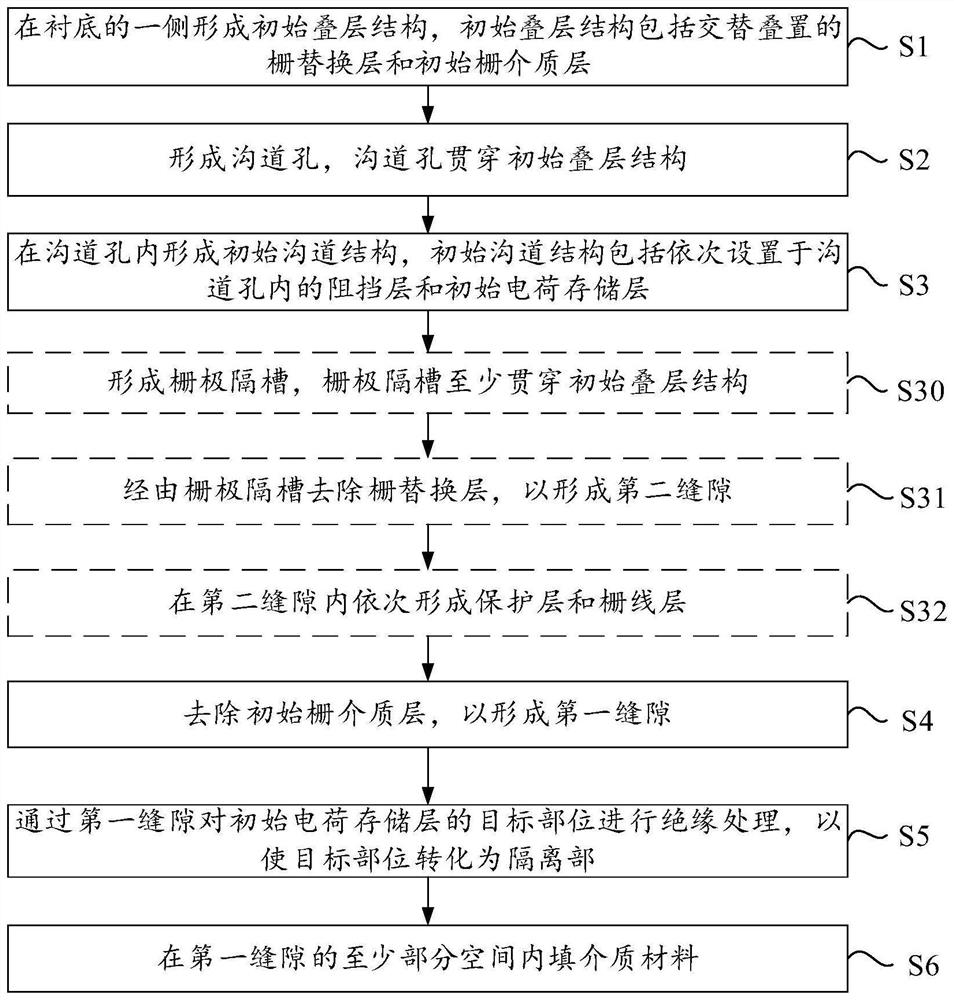

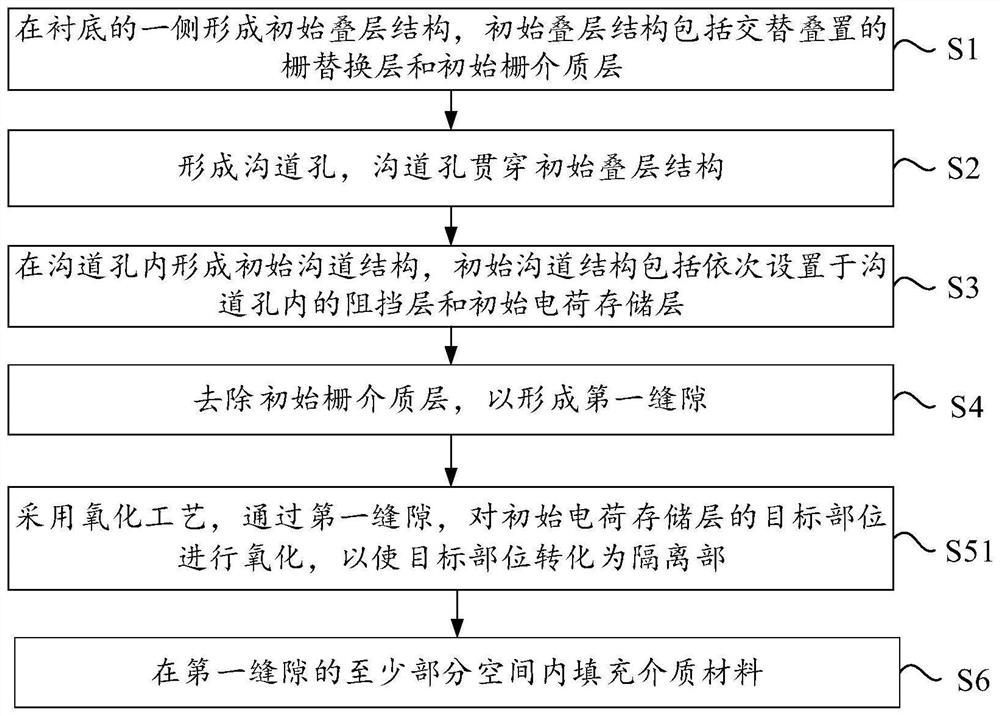

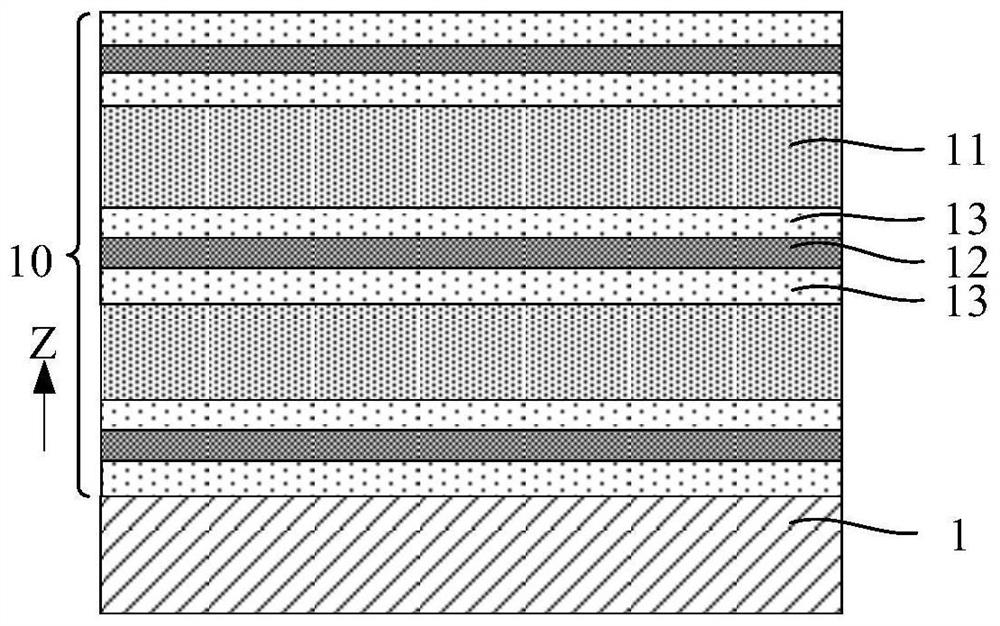

Semiconductor structure and preparation method thereof, three-dimensional memory and storage system

PendingCN114551457AInhibit migrationImprove stabilitySolid-state devicesRead-only memoriesGate dielectricSemiconductor structure

Owner:YANGTZE MEMORY TECH CO LTD

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Try Eureka

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap